# Application Note 4 Timing Analysis for Bipolar Arrays

CHAP 11 - APPLICATION NOTE 4

TIMING ANALYSIS FOR BIPOLAR ARRAYS

There has been a significant specification change for the Q3500 series since this application note was first drafted.

The fanout limits were changed as follows:

S option FROM 6 TO 9 loads

L option 3 4

H option 6 9

3-state drivers 12 8

drivers 15 15

The application note will be redone ASAP. In the meantime, corrections have been indicated.

JANUARY 1985

AMCC reserves the right to make changes to any products herein to improve the reliability, function or design. AMCC does not assume any liability arising out of the application or use of any product or circuit described herein; neither does it convey any license under its patent rights nor the rights of others.

A M C C

APPLIED MICRO CIRCUITS CORPORATION

COPYRIGHT C 1985 ALL RIGHTS RESERVED

## INDEX TO APPLICATION NOTE 4

Timing Analysis is Required Design Guide Specification - what's there Intrinsic Tpd Delay Macro Options Design Guide is the Reference Path Propagation Delay Table of Worst-Case Multiplication Factors TTL Input Typical Tpd Delays: Q700, Q1500 TTL Input Typical Tpd Delays - All Arrays Typical Loading Delay Table of Delta tpd+/tpd- Due to Loads Typical Wire-Or Delay Table of Delta tpd+/tpd- Due to WIREORn Q1500 Example (single macro) Pulse Distortion Example Fanout Limitations (Macro Loading Limits) Fanin Restrictions - How Noted Table of Fanout Restrictions by Array Series and Macro Type High-Capacitive Loading on Output Macros - All Arrays Propagation Delay Multiplication Factors Table of all Multiplication Factors Commercial Specification Military Specification Metal Delays (etch delay) Table of Typical Metal Delays Computing Propagation Delay - the method Pulse Stretch, Shrink Effect of Loading on the Rising/Falling Edge Figure for Pulse Stretch/Shrink Intrinsic Set-up, Hold and Recovery Time Intrinsic Pulse Width Selecting Critical Paths Q700 Example - Timing for the Example

- Schematic for the Example

- PERT chart analysis for the Example

Q1500 Example Q3500 Example

- Timing

- Schematic

# APPENDIX A MISCELLANEOUS CONSIDERATIONS

# Deleter- See Design Guides

#### APPENDIX B

Q700 Examples

1. 15 loads distributed on P-option buffers

2. 15 loads on a High-fanout driver

3. 4-Bit Twisted Tail Mobius, Ring, Johnson counter

4. 4-Bit preloadable counter

Q1500 Example

1. 8-Bit Up-Down Counter

Q3500 Example

1. High-Speed TTL I/O

# TIMING ANALYSIS FOR THE AMCC Q700, Q1500, Q3500 SERIES LOGIC ARRAYS

Prior to schematic capture, a preliminary analysis of the critical paths of a circuit is usually performed to assure that the circuit may be placed on a given array.

A detailed timing analysis of a circuit and its critical paths is required before a circuit can be submitted for place and route.

Timing analysis of a circuit generally includes: worst-case path propagation delays for both rising and falling edge inputs for all critical or suspected critical paths; external/internal set-up, hold and recovery time; pulse skew/tracking due to placement (process variation); pulse distortion due to wire-OR and fanout loading (pulse stretch, pulse shrink); and the maximum frequency of operation (worst-case).

If a DAISY, MENTOR or VALID engineering workstation (EWS) is used for schematic capture, timing analysis is supported by the simulation portions of the EWS software. On the DAISY, for example, the DAISY TIMING VERIFIER (DTV) is used to measure propagation delays, perform timing checks, and to evaluate overall circuit timing.

- Loading and wire-OR delays are added to the basic circuit information file using the Timing Calculator (TCAL) package.

- Metal length delays are added after layout using the AMCC BACK-ANNOTATION software package.

#### DESIGN GUIDE SPECIFICATION

The AMCC design guides for the Q700 logic array series, the Q1500/QH1500 logic arrays and the Q3500 logic array series include the description of the macro libraries for those arrays. The EWS macro graphics are provided with the typical propagation delays, typical current dissipation, along with worst-case set-up, hold and recovery times.

# DAISY: must use component wire-ors

## Front annotation is under Btest: Back annotation

is also under Btest.

# INTRINSIC Tpd DELAY

The propagation delay specifications in the macro library documentation are typical delay times. The propagation delays given for the input, buffer, and internal logic macros are for unloaded macros. Output macros are specified for 15pf load (TTL outputs) or 5pf load (ECL outputs).

#### MACRO OPTIONS

The Q700 library has a power (P) option in addition to the standard (S) version of many of its macros (drivers excepted). In most of the specifications, the Tpd specification appears in the S column only. The Tpd parameters for the P option macro are identical to those of the S option macro. The only parameters which change between them are the current drain and the fanout limitation.

The Q1500/QH1500 library has a power (P) option and a high-speed (H) option in addition to the standard (S) option of many of its macros. The Tpd parameters for the P option macro are identical to those of the corresponding S option macro, while current and fanout restrictions are increased.

The Q3500 library has a low-power (L) option and a high-speed (H) option in addition to the standard (S) version of most of its macros. In this design guide the timing is listed in each column. The fanout for the H and S options is 6 loads and the fanout for the L option macros is 3 loads.

#### DESIGN GUIDE IS THE REFERENCE

The graphic symbol on the DAISY, MENTOR and VALID libraries currently shows the unloaded propagation delay in the upper right corner if there is only one path through the circuit. No propagation delay appears on the macro if there are different delays for different paths. Future versions of the libraries will delete this information from the graphic symbol.

In any case, the designer must reference the design guide. It should always be the overriding reference for the macro parameters.

# PATH PROPAGATION DELAY

Computation of the propagation delay for a circuit path involves an evaluation of the following: input, buffer, logic and output macro propagation delays (Tpd, Tpd+, Tpd-); loading (fanout, wire-OR) on each macro in the path (tpd+, tpd-); capacitive loading on the output macros (delta-Tpd); circuit classification (COMMERCIAL, MILITARY); circuit I/O mode (TTL, ECL, TTLMIX); set-up, hold or recovery times as they affect the path; and an estimate of the metal (etch) delays.

For front annotation, multipliers which approximate the metal delay are used. After layout (auto-place and auto-route) the actual etch lengths are known and can be substituted. (Translator partion)

For the Q700 and Q1500 series arrays, TTL inputs will use a different multiplier than the other macros for propagation and set-up and hold computations. For the Q3500 series arrays, the multiplier for the TTL input macros is the same as for the rest of the macros.

TABLE 12 WORST-CASE DELAY MULTIPLICATION FACTORS

- 1.5 --- For COMMERCIAL applications (ALL BUT TTL INPUT MACROS) 0°C to 70°C, ±5% power supplies

- 2.0 --- FOR TTL INPUTS COMMERCIAL APPLICATIONS

- 1.6 --- For MILITARY applications (ALL BUT TTL INPUT MACROS) -55°C ambient to +125°C case +10% power supplies

- 2.5 --- FOR TTL INPUTS MILITARY APPLICATIONS

Tpd | typical \* M.F. = Tpd | worst-case

# TTL INPUT TYPICAL Tpd DELAYS - 0700, 01500 ARRAYS ONLY

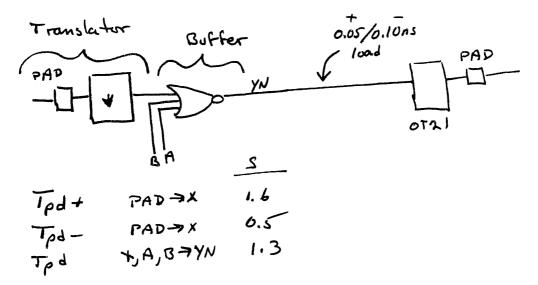

Circuits with TTL input macros will need to group the TTL input propagation delay serarate from the propagation delays of all other macros since the TTL macros will use a different worst-case commercial or military multiplier (2.0 or 2.5) from the rest of the macros in the path (1.5 or 1.6). Where a buffer or logic/buffer is included in the input macro, as for the Q1500 series macros, the macro will be specified with two sets of Tpd delays, one group for the input translation which will use the larger multiplier, and one for the logic/buffer which will use the same multiplier used with the rest of the macros in the path.

## TTL INPUT TYPICAL Tpd DELAYS - ALL ARRAYS

TTL input macros are provided with a rising edge and a falling edge propagation delay. Any circuit which uses 100% TTL or TTLMIX input macros <u>must</u> compute both the rising edge input and falling edge input path delays. Asymmetrical set-up and hold times must also be evaluated.

100% ECL circuits should also compute rising and falling edge input delays for propagation delay and set-up and hold time.

#### TYPICAL LOADING DELAY

Once the macro propagation delays are listed, the next step in performing timing analysis on a circuit designed for any of the arrays in the Q700, Q1500 or Q3500 series is to evaluate the loading for each macro in the circuit path. The typical risers edge delays due to load (tpd+) and the typical falling edge delays due to load (tpd-) are listed in the table below.

| TYPICAL | PROPAGATION | DELAY DUE TO | LOADING |

|---------|-------------|--------------|---------|

| Array   | Macro       | tpd+         | tpd-    |

| Series: | Option:     | ns/load      | ns/load |

| Q700:   | S           | 0.05         | 0.10    |

|         | P           | 0.05         | 0.10    |

|         | Driver      | 0.05         | 0.10    |

| Q1500:  | S           | 0.05         | 0.10    |

|         | P           | 0.05         | 0.10    |

|         | H           | 0.05         | 0.10    |

|         | Driver      | 0.05         | 0.10    |

| Q3500:  | S           | 0.03         | 0.05    |

|         | L           | 0.03         | 0.10    |

|         | H           | 0.03         | 0.05    |

|         | Driver      | 0.03         | 0.03    |

Multiple output macros could have different loads on each output and each output will belong to a separate timing path.

#### TYPICAL WIRE-OR DELAY

The wire-OR loading, if any wire-ORs appear in the path, must also be considered. The typical risengelye delays due to wire-OR connections (tpd+) and the typical falling edge delays due to wire-OR connections (tpd-) are listed in the table below.

There are significant differences in the Q3500 family in the sense that tpd+ is slower than tpd-, the reverse of the Q700 and Q1500 series logic arrays. This is because of the high resistance of the oxide ISO process. The tpd- actually becomes faster as more outputs are wire-ORed due to more current capacity. The Q3500 series is limited to low-power options only for WIREOR4.

Other concerns, do not wire-OR mixed options, do not wire-OR high-fanout drivers, do not cascade wire-ORS and honor individual macro restrictions.

TYPICAL PROPAGATION DELAY DUE TO WIRE-OR

| Array<br>Series: | Net<br>Size:                  | tpd+<br>ns           | tpd-<br>ns           |                                                   |

|------------------|-------------------------------|----------------------|----------------------|---------------------------------------------------|

| Q700:            | WIREOR2<br>WIREOR3<br>WIREOR4 | 0.05<br>0.10<br>0.15 | 0.10<br>0.20<br>0.30 | (limit, S or P option)                            |

| Q1500:           | WIREOR2<br>WIREOR3<br>WIREOR4 | 0.05<br>0.10<br>0.15 | 0.10<br>0.20<br>0.30 | <pre>(limit P, H options) (limit, S option)</pre> |

| Q3500:           | WIREOR2<br>WIREOR3<br>WIREOR4 | 0.10<br>0.20<br>0.30 | 0.05<br>0.05<br>0.05 | (limit for S, H) (limit for LP option)            |

|                  |                               |                      | /                    |                                                   |

AMCC HIGH PERFORMANCE LOGIC ARRAY DESIGN SEMINAR

TIMING ANALYSIS - Q700, Q1500, Q3500 SERIES ARRAYS JANUARY 1985 - DATED MATERIAL

#### O1500 EXAMPLE

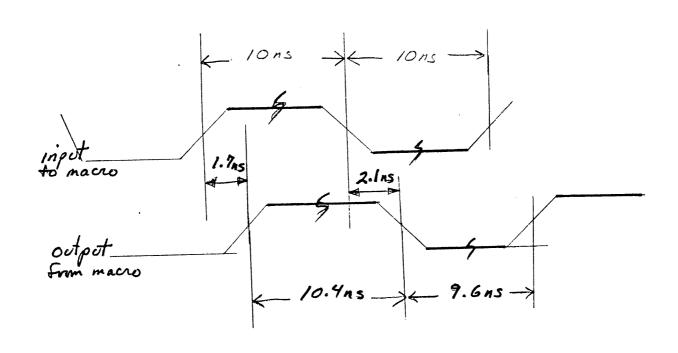

For example, if a Q1500 macro has an unloaded propagation delay (Tpd) of 1.3ns, is wire-ORed with two other sources (WIREOR3) and fans out to six loads, the total net is:

$^{2}$  (# of wire-or inputs - 1) +  $^{6}$  (load outputs) =  $^{8}$  wires total.

- The added delay due to loading is:

- 8 \* 0.05 = 0.40ns for the rising edge.

- 8 \* 0.10 = 0.80ns for the falling edge.

- The rising edge delay through the loaded macro totals:

1.3 + 0.4 = 1.7ns TYP

- The falling edge delay through the loaded macro totals: 1.3 + 0.8 = 2.1 ns (one decimal place accuracy)

#### PULSE DISTORTION

For heavily loaded paths, the designer should alternate the signals through inversion to cancel the cumulative effect of the difference between rise and fall delays. Otherwise, pulse stretch and pulse shrink become areas of concern and can lower the maximum operating speed for the circuit such as the case when the pulse shrink results in a pulse that falls below the minimum pulse width requirements for a macro.)

TYPICAL PROPAGATION DELAY THROUGH 1 MACRO, Tpd=1.3ns, 6 LOADS, WIREOR3

AMCC HIGH PERFORMANCE LOGIC ARRAY DESIGN SEMINAR

TIMING ANALYSIS - Q700, Q1500, Q3500 SERIES ARRAYS JANUARY 1985 - DATED MATERIAL

#### FANOUT LIMITATIONS

Different macros have different loading limitations, as summarized in the table shown on the next page. Loading limits for clock paths and distortion-sensitive paths should be derated by 20%. Fanout violations or fanout in excess of derated levels should be checked when performing the timing analysis.

#### FANIN RESTRICTIONS

The loading that a typical macro presents to its driving source is one load. For those cases where the fanin is greater than one, an "\*" is used on the pin (on the EWS graphic) and a notation is made in the design guide.

Some macros look like they present two or more loads to their driving source when they do not. In this case an "\*" is used on the pin and a notation is made in the design guide.

Q700 TTL output macros being driven by internal logic (100% TTL mode) require that the fanout of their driving source be derated. This is equivalent to the output macros having a fanin of three. The Q700 design guide in the future will carry an "\*" and a comment on these macros.

| Q700             | FANIN: |                                         |

|------------------|--------|-----------------------------------------|

| OUTPUT<br>OTHERS |        | 3 LOADS<br>1<br>exceptions as specified |

AMCC HIGH PERFORMANCE LOGIC ARRAY DESIGN SEMINAR

TIMING ANALYSIS - Q700, Q1500, Q3500 SERIES ARRAYS JANUARY 1985 - DATED MATERIAL

# FANOUT RESTRICTIONS: (STANDARD/DERATED)

| (STANDARD/DERATE                                                                                                                       |                                             |                                                  |            |

|----------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|--------------------------------------------------|------------|

| Q700 Series                                                                                                                            | Macro Op<br>S                               | ption:<br>P                                      |            |

| Unbuffered input macros Input buffers Logic Output buffers Output macros D cell drivers Three-state enable drivers High-fanout drivers | 16<br>8<br>15/12                            | 9/7<br>9/7<br>9/7<br>DATA SHEET                  |            |

| Q1500 Series                                                                                                                           | S                                           | P                                                | H          |

| Three-state enable drivers                                                                                                             | 6/4<br>6/4<br>1<br>REFER TO<br>5 8<br>15/12 | -<br>6/4<br>9/7<br>DATA SHEET<br>-<br>-          | _          |

| Q3500 Series                                                                                                                           | S                                           | L                                                | H          |

| Three-state enable driver                                                                                                              | 9/7<br>9/7<br>1<br>REFER TO<br>s 8<br>15/12 | -<br>4/3<br>4/3<br>-<br>DATA SHEE'<br>8<br>15/12 | 8<br>15/12 |

<sup>•</sup> Latch output may be restricted from wire-OR - check the individual macro documentation

<sup>•</sup> Unbuffered input macros cannot be wire-ORed

<sup>•</sup> Output buffers cannot be wire-ORed

# HIGH-CAPACITIVE LOADING ON OUTPUT MACROS - ALL ARRAYS

The design guides specify that timing is given for a 15pf load for TTL output macros and a 5pf load for ECL macros. TTL outputs can handle up to 50pf loading at a cost of 2.0ns per timing parameter for the added 35pf load. ECL outputs with high capacitive loading will add 80ps (0.08ns) to each timing parameter per each lpf over the specified 5pf load.

# PROPAGATION DELAY MULTIPLICATION FACTORS

All of the tables shown in this note and all of the macro propagation delay specifications given in the design guides provide typical propagation delays. To perform worst-case analysis, the following multipliers must be used.

|                        | WORST-CASE MUI             | TIPLICATION F                       | ACTORS            |  |

|------------------------|----------------------------|-------------------------------------|-------------------|--|

| Circuit<br>Classificat | Array<br>ion: Series:      | Macro<br>Type:                      | M.F.              |  |

| Nominal                | any                        | any                                 | 1.0               |  |

| Commercial             | Q700;Q1500<br>Q3500<br>any | TTL franslators TTL input any other | 2.0<br>1.5<br>1.5 |  |

| Military               | Q700,Q1500<br>Q3500<br>any | TTL translators TTL input any other | 2.5<br>1.6<br>1.6 |  |

| Minimum                | any                        | any                                 | 0.7*              |  |

<sup>\*</sup> Guideline only; not guaranteed

These multiplication factors take into account the following:

- Process variations (~30%);

- Temperature variations (~25%);

- Voltage variations (~20%);

- Signal skew;

- Package pin delays;

- Metal length or macro-macro metal delay, both layers, (~10%). An assumption (100mils/net) is made as to the maximum etch length (first and second layer metal) that will occur. This assumption will hold for all typical connections. Etch runs that wander around the chip (edge to edge, for whatever reason) will experience a longer delay. Most of the actual etch runs will, in fact, experience a shorter delay. The front annotation multiplier was designed to be conservative.

#### COMMERCIAL SPECIFICATION

Commercial worst-case multipliers are for  $0^{\circ}\text{C}$  to  $70^{\circ}\text{C}$  with  $\pm 5\%$  power supply variation.

#### MILITARY SPECIFICATION

Military worst-case multipliers are for  $-55^{\circ}\text{C}$  ambient to  $+125^{\circ}\text{C}$  case with  $\pm 10$ % power supply variation. MIL-STD-883C Class B screening is used.

#### METAL DELAYS

Metal delays are known after layout. When the metal length for a net exceeds 100 mils, then the added delay due to the etch length over 100 mils must be added into both propagation delay and set-up and hold-time comptations.

| TYPICAL | METAL | DELAYS | (ps/mil) |  |

|---------|-------|--------|----------|--|

|---------|-------|--------|----------|--|

| Technology:                                                     | Juncti<br>Isolat          |                              | Oxide<br>Isola           | ated        |

|-----------------------------------------------------------------|---------------------------|------------------------------|--------------------------|-------------|

| Array Series:<br>Macro Option:<br>First Metal:<br>Second Metal: | Q700<br>S,P<br>7.0<br>4.0 | Q1500<br>S,P,H<br>7.0<br>4.0 | Q35<br>S,H<br>5.0<br>3.5 | 10.0<br>7.0 |

Metal length as accounted for in the worst-case multipliers is assumed to be 100mils/net MAXIMUM. For circuits with longer etch runs, adjustments must be made for the additional delay. A BACK-ANNOTATION program is being developed by AMCC to assist in verification of worst-case paths using actual etch metal lengths as computed by QUASAR (post-layout).

AMCC HIGH PERFORMANCE LOGIC ARRAY DESIGN SEMINAR .

TIMING ANALYSIS - Q700, Q1500, Q3500 SERIES ARRAYS JANUARY 1985 - DATED MATERIAL

# COMPUTING PROPAGATION DELAY

Once the input, buffer, internla logic and output macro propagation delays, loading and wire-OR delays and high-capacitive output macro loading delays are known, the maximum worst-case is computed by:

- Compute the propagation of the falling edge input.

The falling edge is typically the worst-case,

depending on the alternation of the signal switching.

- Sum the individual macro delays in the path is question. For TTL, TTLMIX circuits, keep the TTL input macro pad->buffer delay (Tpd-) as a separate sum.

- Adjust output macro delays according to the capacitive loading.

- Add the tpd+ or tpd- loading delay (as appropriate) for each input and internal macro. Every connected macro has at least one load

- Add the tpd+ or tpd- wire-OR loading (as appropriate) for any wire-OR in the path.

- IF METAL LENGTHS ARE KNOWN (after routing) add in the metal delays. (Backannotation only.)

- Multiply the sums by the appropriate multiplication factor.

- Add any Tsu, Th or Trec (set-up, hold or recovery time)

that affects the path.

- Repeat the process for the rising edge input.

For the TTL, TTLMIX input macros, use Tpd+.

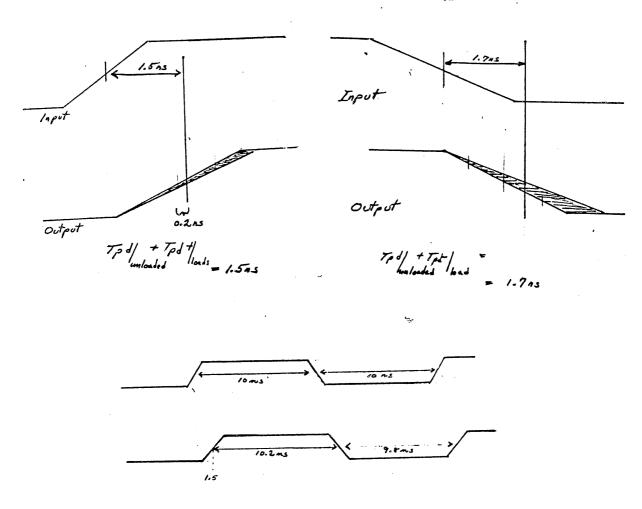

#### PULSE STRETCH. PULSE SHRINK

Compare the results for each path for input rising edge propagation delay and for input falling edge propagation delay. Verify that the minimum pulse width requirements of the latch and flip/flip macros are not violated. If they are, adjust the propagation delay by the amount needed to allow the specified worst-case minimum pulse width specification to be met.

#### INTRINSIC SET-UP, HOLD AND RECOVERY TIMES

The Tsu, Th and Trec times specified in the design guide for memory macros (latches, flip/flops) are worst-case minimum times and are not multiplied.

#### INTRINSIC PULSE WIDTH

The pulse width (PW) specifications in the design guide are worst-case minimum.

#### SELECTING CRITICAL PATHS

Compute the timing for all paths that can or could be considered to be critical to the circuit operation. A critical path may or may not be the longest path in a circuit. A timing PERT chart is a useful tool for multiple path analysis.

Effect of loading on the rise and fall edges for a single macro, 4 loads. Unloaded Tpd = 1.3ns. Loaded, Tpd (+) = 1.5ns; Tpd(-) = 1.7ns. Pulse shrink is at signal = low at 9.8ns; pulse stretch is at signal = high at 10.2ns.

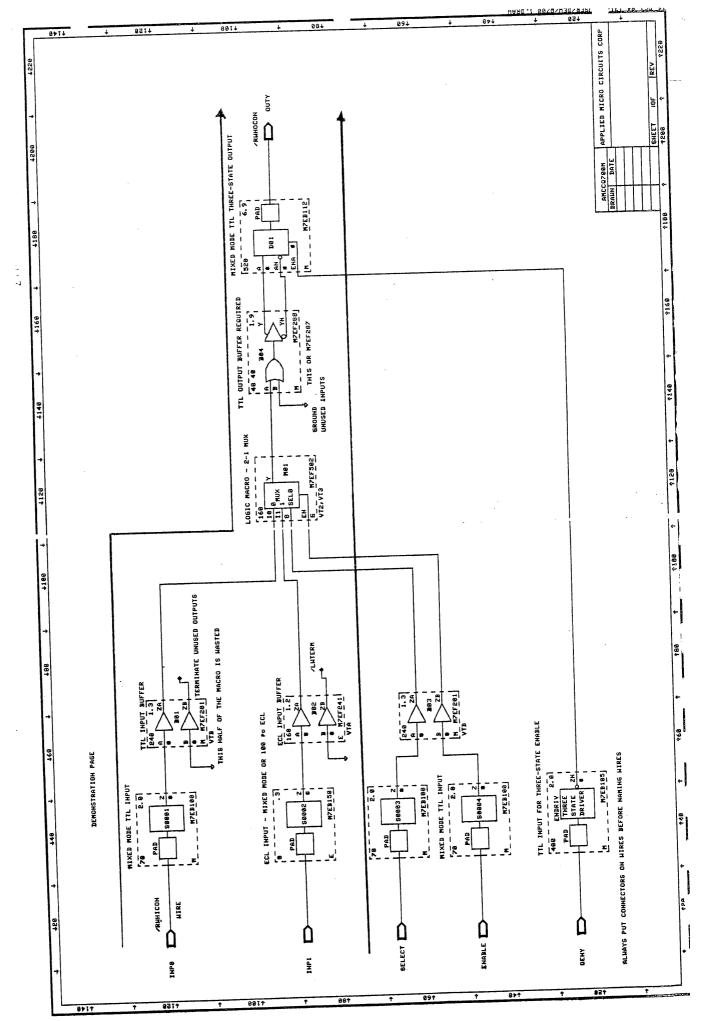

#### O700 EXAMPLE

On the next two pages a sample Q700 TTLMIX circuit is shown along with its PERT chart timing analysis. This technique is useful for evaluating the critical path(s) in a circuit. In this case, the longest path is the SELECT path at 14.4ns (TYP). Assume that the capacitive loading on the output macro is <15pf.

Adding these two together gives 24.93ns worst-case MIL for the rising edge input. Now compute the falling edge input.

```

TTL input Tpd-: 0.5 * 2.5 = 1.25

Loads (total): 4 * 0.10 = 0.4

Buffer EF201: 1.3

MUX select->Y: 2.0

Output buffer: 1.9

Output: 6.9

Total 12.5 * 1.6 = 20.0

```

Adding these two together gives 21.25ns worst-case MIL for the falling edge input.

9700 2:1 MUX EXAMPLE

(MIXED MODE, TYPICAL VALUES)

4-23

#### O1500 EXAMPLE

A Q1500 IT02 input macro is connected to an OT21 output macro. What is the worst-case commercial path? The rising edge delay for the IT02 macro is composed of the Tpd+ of the input level conversion and the Tpd of the buffer which are:

Tpd+ = 1.6ns

Tpd buffer = 1.3ns

There is one load between the ITO2 and the OT21 which contributes 0.05ns. The delay through OT21, assuming that the external capacitive load is <15pf is 7.9ns (buffer and E/T conversion).

The worst case COMMERCIAL rising edge path delay is found by:

$$(1.6) * 2.0 + (1.3 + 0.05 + 7.9) * 1.5 = 17.08$$

ns.

The falling edge delay is:

$$(0.5) * 2.0 + (1.3 + 0.1 + 7.9) * 1.5 = 14.95$$

ns

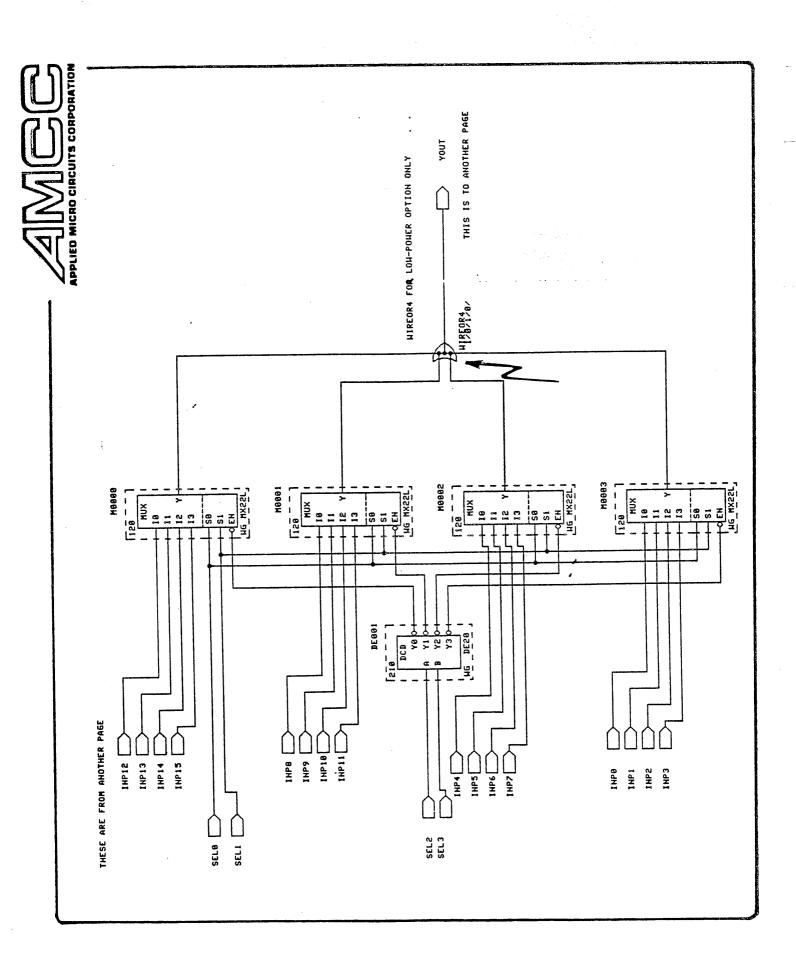

#### O3500 EXAMPLE

A partial circuit, a 16:1 MUX composed of MX22L and DE20 macros is shown on the next page. To compute the time delay from page input to page input, choose the select path through the DE20 macro, through the enable of the MUX, through the WIREOR4 to the YOUT page output. Nothing is given about the loading on YOUT.

| A->Yi DE20  | 0.65                                      |

|-------------|-------------------------------------------|

| 1 load      | 0.03/0.05 (standard macro)                |

| EN->Y MX22L | 1.05 (this is the slow, low-power option) |

| WIREOR4     | .3 /.05                                   |

| Total       | 2.88 rising edge<br>3.25 falling edge     |

Note that the loading tpd+ is different for the Q3500 series and it is option-dependent. A load on the low-power MUX macro would have 0.03/0.10 as its rise/fall time effect.

The worst-case MILITARY path is found by multiplying by 1.6; the worst-case COMMERCIAL path is found by multiplying by 1.5.

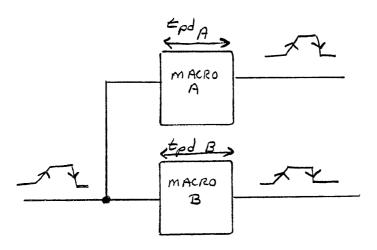

#### INTERNAL SIGNAL TRACKING (SKEW)

Factors which affact the signal delay tracking within the array include such things as relative position within the device, process variation, power supply variations, operating temperature, and the characteristics of the various macros.

As a guideline, identical macros located by auto-place and auto-route, exhibit 20% tracking on the same edge (both edges rising or both edges falling). Using preplacement and prerouting, identical macros, plasced adjacent to each other, will exhibit 5% tracking on the same edge. The rising edge effect is 0.5 of the falling edge effect.

This is important when planning clock and reset distribution to register/counter macros.

Process variations are accounted for in the worst-case multiplication factors.

$\Delta t_{p}J + \equiv \Delta t_{p}J - \left| t_{p}J_{A} - t_{p}J_{B} \right| = 0.2 * t_{p}J_{A}$ (Acr B)

If adjacent, preplaced, prerouted

Dtpd+ = Dtpd- = /tpd - tpdp = 0,05 + tpd/

#### Q700 EXAMPLES

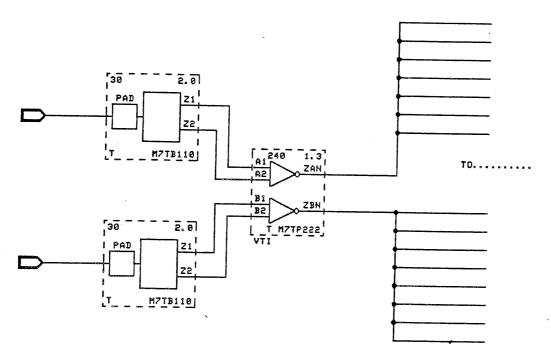

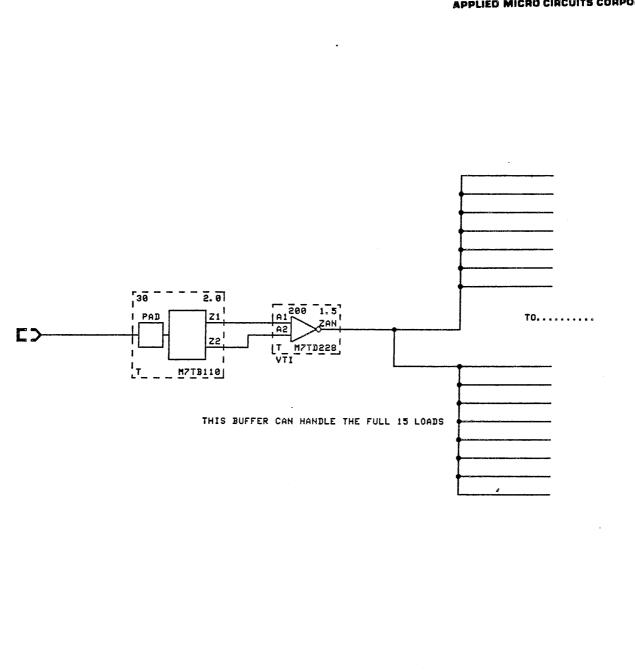

# 1. M7TB110 INPUT, M7TP222 BUFFER, 15 LOADS.

The loads are evenly distributed across two buffers and two input pads are used. The longest path is the one with 8 loads on the buffer. This is a point to point computation for reference and is not a complete circuit.

| M7TB110                      | Rising<br>Typical<br>2.1 | M.F.<br>MIL<br>*2.5 | Falling<br>Typical<br>0.5 |                                           |

|------------------------------|--------------------------|---------------------|---------------------------|-------------------------------------------|

| Worst Case:                  | 5.25ns                   |                     | 1.25ns                    | MILITARY = 2.5 * TYPICAL (TTL Input only) |

| l Load<br>M7TP222<br>8 Loads | 0.05<br>1.3<br>0.4       | *1.6                | 0.10<br>1.3<br>0.8        |                                           |

| Total Worst Case:            | 1.75ns<br>2.8ns          |                     | 2.2ns<br>3.52ns           | MILITARY = 1.6 * TYPICAL                  |

| Total W.C.:                  | 8.05ns                   |                     | 4.77ns                    | Sum                                       |

The total point-to-point path delay, rising edge input, is 5.25 + 2.8 = 8.05ns. The total for the falling edge input is 4.77ns.

EACH BUFFER DRIVES UP TO AND INCLUDING 9 LOADS - THIS 15 LOAD OUTPUT IS SPLIT BETHEEN TWO BUFFERS

## 2. M7TB110 INPUT, M7TD228 DRIVER BUFFER, 15 LOADS

All 15 loads are driven by the high-fanout driver M7TD228. The worst case MILITARY point to point delay is found by:

| M7TB110                       | Rising<br>Typical<br>2.1 | M.F.<br>MIL<br>*2.5 | Falling<br>Typical<br>0.5 |                                           |

|-------------------------------|--------------------------|---------------------|---------------------------|-------------------------------------------|

| Worst Case:                   | 5.25ns                   |                     | 1.25ns                    | MILITARY = 2.5 * TYPICAL (TTL input only) |

|                               |                          | *1.6                |                           |                                           |

| l Load<br>M7TD228<br>15 Loads | 0.05<br>1.5<br>0.75      |                     | 0.10<br>1.5<br>1.5        |                                           |

| Total Worst Case:             | 2.3ns<br>3.68ns          |                     | 3.lns<br>4.96ns           | TYPICAL MILITARY = 1.6 * TYPICAL          |

| Total W.C.:                   | 8.93ns                   |                     | 6.21ns                    | Sum                                       |

The total point-to-point path delay, rising edge input, is 5.25 + 3.68 = 8.93ns. The total for the falling edge input is 6.21ns.

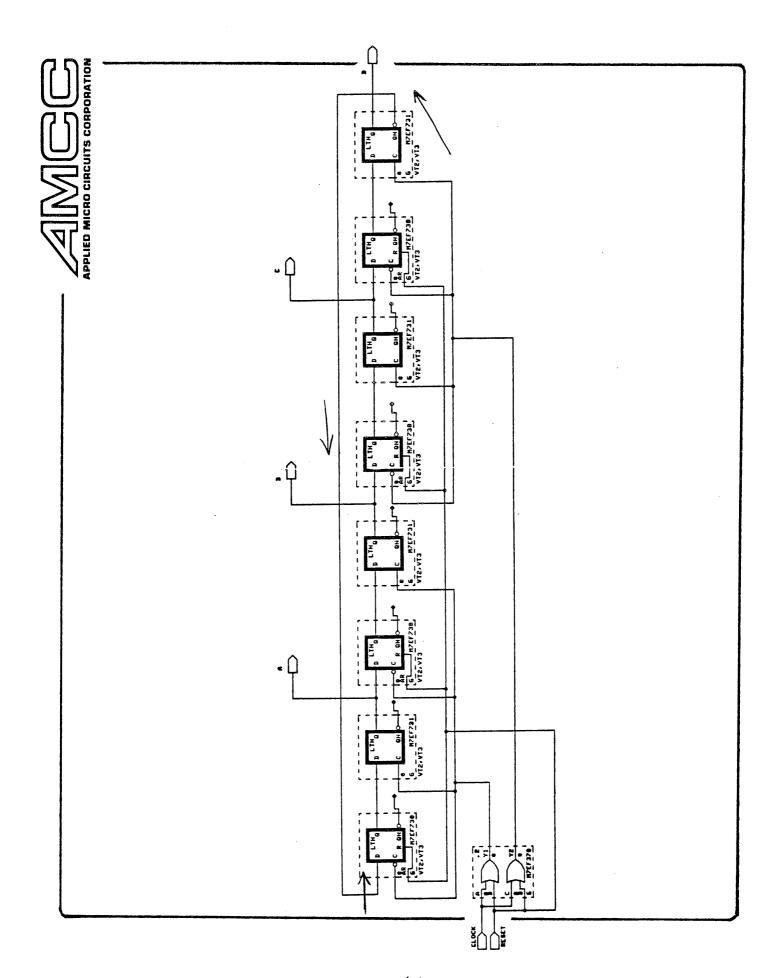

### 3. 4-BIT TWISTED TAIL (MOBIUS, RING, JOHNSON) COUNTER

The timing for this circuit depends on the required delay between rising clock edges. The input time for the input macro and clock buffer do not matter so long as they total less than the worst-case path computed below. The worst-case is the clock-to-output of the last stage M7EF731, the loading on QN (2 external loads assumed on all Q, QN although they are not shown), and the intrinsic set-up time for the first stage M7EF730.

Since no TTL input is invloved, the COMMERCIAL worst-case multiplier is 1.5 and the MILITARY worst-case multiplier is 1.6 for all macros and loads shown.

| Clock->QN<br>3 Loads<br><sup>T</sup> set-up | Rising<br>1.7<br>0.15<br>2.0 | Falling<br>1.7<br>0.3<br>2.0 |                     |   |     |   |         |

|---------------------------------------------|------------------------------|------------------------------|---------------------|---|-----|---|---------|

| Total: Worst-case:                          | 3.85<br>6.16                 | 4.0ns<br>6.4ns               | TYPICAL<br>MILITARY | = | 1.6 | * | TYPICAL |

The speed of this circuit is: 1 / 6.4 = 156.25 MHz (worst-case MILITARY).

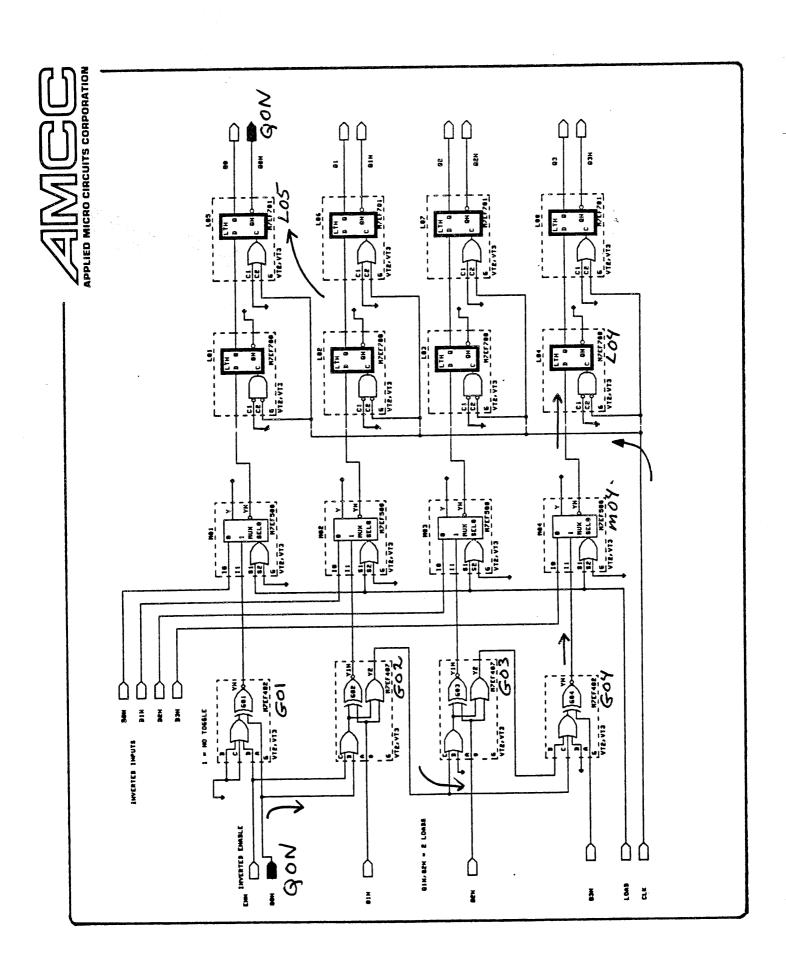

#### 4. 4-BIT PRELOADABLE COUNTER

For this circuit, the rising edge to rising edge delay is also of the most interest. The worst-case (longest) path at first glance appears to be the QON generation, fed back to the EXNOR gate GO1. Tracing this path produces:

| INPUT:                                                                                                                                                                          | RISING<br>ns                    | FALLIN<br>ns                     | īG                             |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|----------------------------------|--------------------------------|

| Clock->Q0N L05 (M7EF701) Q0N Loads = 2 loads Tpd G02 (M7EF407) B->Y2 G02 Loads = 2 loads Tpd G04 (M7EF402) C->YN G04 Loads = 1 load Tpd M04 (M7EF500) I1->YN M04 Loads = 1 load | 2.0<br>0.1<br>2.0<br>0.1<br>1.2 | 2.0<br>0.2<br>2.0<br>0.05<br>1.2 | falling falling rising falling |

| Total  • Worst case Typical * 1.6 =                                                                                                                                             | 7.55<br>12.08                   |                                  | TYPICAL<br>MILITARY            |

| Tsetup L04 (M7EF700)                                                                                                                                                            | 2.0                             | 2.0                              | MIN                            |

| • Worst case TOTAL:                                                                                                                                                             | 14.08                           | 14.40                            | MILITARY                       |

With a rising-edge to rising-edge delay of 14.40ns worst-case MILITARY, the speed of operation is 69.44MHz. If there are additional loads on QON on another page then they must also be factored into the computation before a final value for the path delay can be given. One additional load would add 0.1ns to the time path, and reduce the speed to 68.7MHz.

#### Q1500 EXAMPLE

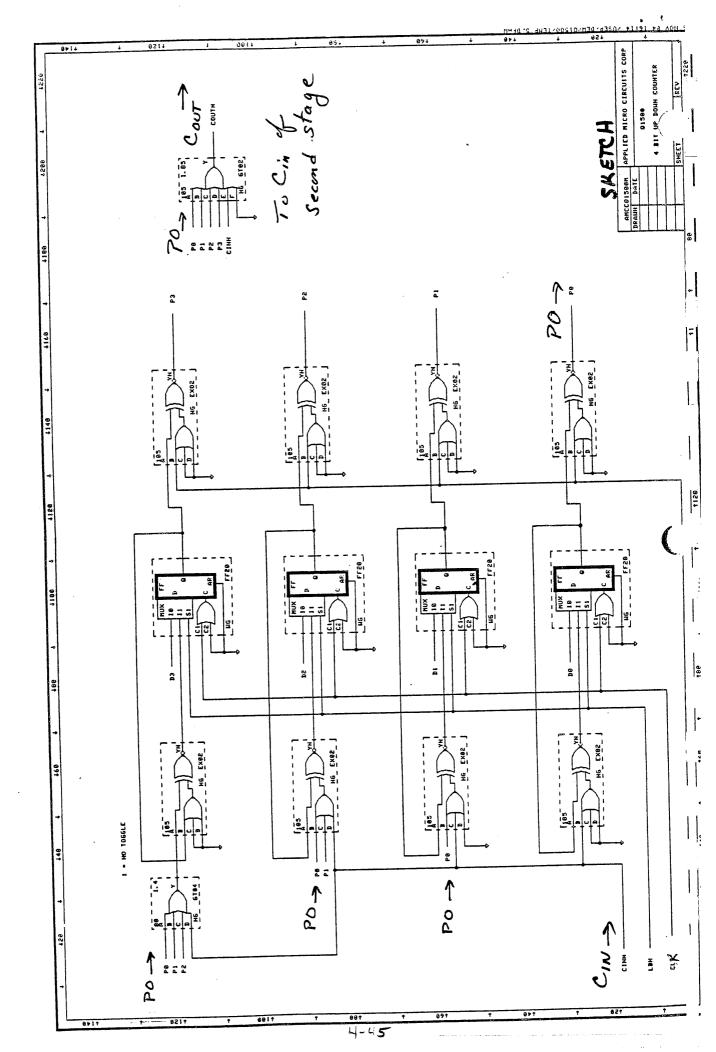

#### 1. 8-BIT UP/DOWN COUNTER

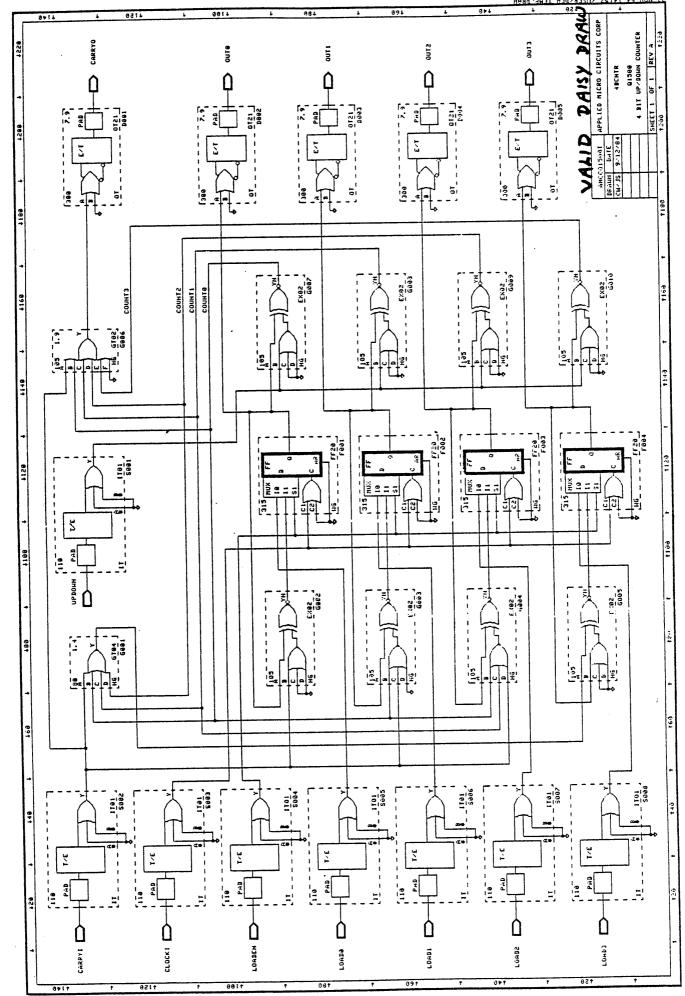

A 4-Bit up/down counter is shown on the following page. (This sketch is not a complete EWS schematic.) A complete 4-bit DIASY schematic is shown on the page following the sketch. (FF20 is an older macro, replace with TBS.)

To build an 8-bit up/down counter, connect two 4-bit counter stages through the  $\rm C_{out}$  of the least significant bit stage to the  $\rm C_{in}$  of the most significant stage.

Timing for an 8-bit counter is found as follows:

| First stage:                                                    |        |             |

|-----------------------------------------------------------------|--------|-------------|

| Clock->Q F/F                                                    | 2.0    |             |

| 3 Loads (counting output macro)                                 | 0.3    | falling     |

| Tpd EX02 A->YN                                                  | 1.3    | _           |

| 4 Loads (PO generation)                                         | 0.2    | rising      |

| Tpd GT02 (Cin generation)                                       | 1.9    | _           |

| Second Stage:                                                   |        |             |

| Tpd GT04                                                        | 1.4    |             |

| l Load                                                          | 0.05   | rising      |

| Tpd EX02 A->YN                                                  | 1.3    |             |

| ent care fine fine firm care care care care care care care care |        |             |

| Total:                                                          |        | ns TYPICAL  |

| Worst Case = 1.6 * TYPICAL =                                    | 13.52r | າຣ          |

|                                                                 |        |             |

| Tsetup F/F                                                      | 2.0    |             |

| Motol moth delaware                                             |        |             |

| Total path delay:                                               | 15.52  |             |

| Maximum operating frequency:                                    | 64.4N  | Hz MILITARY |

| <u> </u>                                                        | . •    |             |

4-46

- If the carry out of the first stage must go out to another chip (through an output macro), then additional loading must be shown for that load.

- If the two halves of the counter are for some reason on two different arrays, there is a considerable delay through the input and output macro stages (including input and output buffers). The two segments of the counter should be kept on the <u>same array</u>.

Verifying that this is the worst-case path is left as an exercise.

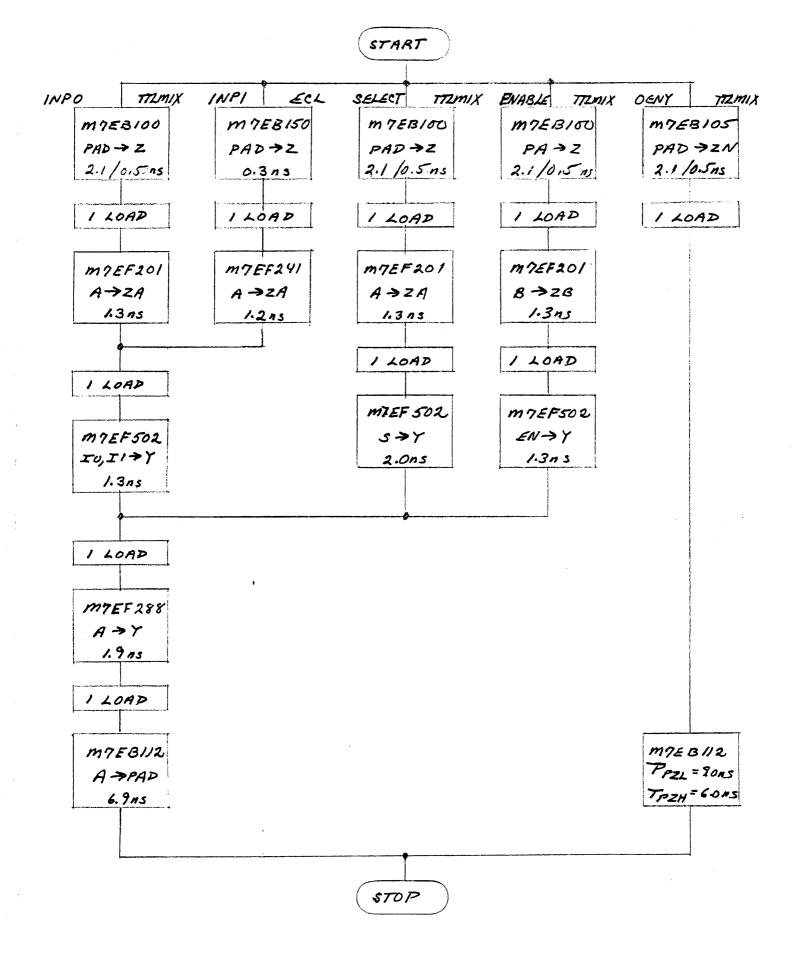

#### Q3500 EXAMPLE

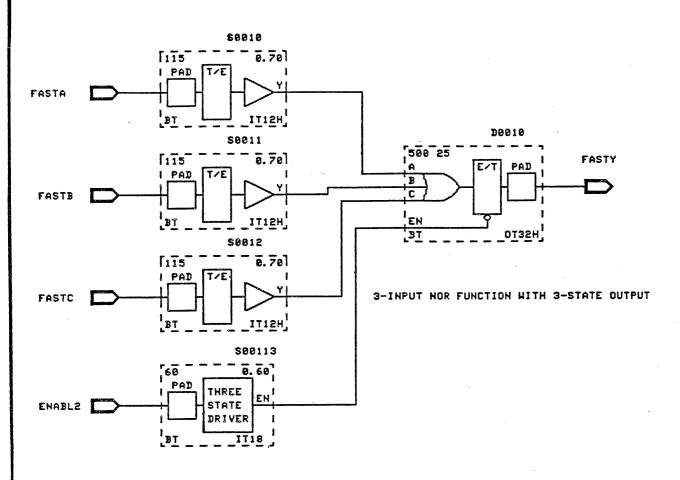

#### 1. HIGH-SPEED TTL I/O

The simple 3-input OR TTL I/O function on the next page uses H-option macros from the Q3500 library. Worst-case timing is the delay through ITl8 and the EN->PAD Tpd for OT32H.

| SUMMARY | :              | Rising | Falling |

|---------|----------------|--------|---------|

| IT12H   | PAD->Y Tpd     | 2.8    | 0.6ns   |

| IT18    | PAD->Y Tpd     | 2.7    | 0.2ns   |

| OT32H   | A,B,C->PAD Tpd | 3.9    | 3.9ns   |

| OR32H   | EN->PAD Tpd    | 5.9    | 5.9ns   |

| l load  | S option _     | 0.03   | 0.lns   |

| l load  | H option       | 0.03   | 0.5ns   |

FASTA path = 2.8 + 0.03 + 3.9 = 6.73 ns TYPICAL ENABL2 path = 2.7 + 0.03 + 5.9 = 2.63 ns TYPICAL

If ENABLE2 had been input to an IT18H:

IT18H PAD->Y Tpd 0.8 0.2ns

Then:

ENABLE2 path = 0.8 + 0.03 + 5.9 = 6.73ns TYPICAL

#### Naming

Adder Buffer Gate Exclusive or/nor Mux DE Decoder Flip flop = Latch Memory module MM MI\_\_\_ MSI macro Special cell = LS = Inputs Outputs Bidirectional I/O BD Wireors None of the above Therefore, the circuit should have used the H option for the three-state enable driver IT18. Additional loads on IT18 would add to the path propagation delay.

Worst case delay is 1.6 \* 7.0  $\approx$  11.2ns MILITARY worst-case. The Q3500 series has only one multiplier for MILITARY (1.6) and one for COMMERCIAL (1.5).

The Q3500 series library is the only one providing a high-speed option for the three-state enable drivers.