6195 LUSK BLVIL San Diego, CA 92121 16193 430-9333 TWX-TELRX 910-337-1136

FAX 619-450-9685

Dear AMCC Customer,

We are pleased to provide you with the ANCC MacroMatrix software for the Q14000 BiCMOS Logic Array Series, which includes the macro library and design support software. We are excited about this new technology which provides the benefits of having speed, high density and low power on the same chip.

The macro library and design manual are individually registered to you. To request another copy of the Q14000 Design Manual, contact your local AMCC sales representative. A Q14000 Design Guide is available for those not actively doing a design.

Should you require additional assistance, please do not hesitate to call any of our application engineers at (619) 450-9333.

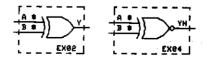

### Volume I Q14000 Series

## BiCMOS Logic Arrays

Applied MicroCircuits Corporation

### Q14000 BiCMOS Series Design Manual

Includes: Q2100B, Q9100B BiCMOS Logic Arrays

The material in this document supercedes all previous documentation issued for the Q14000 BiCMOS Series Logic Arrays

AMCC reserves the right to make changes to any product herein to improve the reliability, function or design. AMCC does not assume any liability arising out of the application or use of any product or circuit described herein, neither does it convey any license under its patent rights nor the rights of others.

AMCC and MacroMatrix are registered trademarks of Applied MicroCircuits Corporation.

# Section 1: Introduction

| INTRODUCTION | (803) |

|--------------|-------|

| INTRODUCTION | (803) |

| Table of Contents 1-2                        |

|----------------------------------------------|

| Introduction 1-3                             |

| Q14000 Series Description 1-6                |

| Typical Applications 1-9                     |

| Features 1-9                                 |

| Figure 1-1 Design Interface and Support 1-11 |

| Table 1-1 Supported Arrays 1-3               |

| Table 1-2 Array Density 1-7                  |

### INTRODUCTION

This design manual provides a summary of the AMCC (Applied Micro Circuits Corporation) Q14000 Series BiCMOS Logic Arrays. Volume 1 is composed of the following sections:

- Section 1: Introduction

- Section 1: Introduction

Section 2: Design Methodology

Section 3: Timing Analysis

Section 4: External tgu, th

Section 5: Power/Packaging

Section 6: Macro Library Documentation

- Section 6-1: TTL Interface

Section 6-2: TTLMIX Interface

Section 6-3: ECL Interface

- Section 6-4: Internal Logic Macros

- Section 6-5: Special Macros

- Section 7: QuicksheetsSection 8: Index

It also includes information on:

- Product features

- Performance specifications

- · Design Interface and support

and contains a listing of the macros currently available. The AMCC Packaging Brochure should also be referenced for further information on packaging.

The Q14000 Series supports the following arrays:

TABLE 1-1 SUPPORTED ARRAYS

- Q9100B

- Q2100B

Volume 1 of this design manual is intended as a self-contained design aid to allow the proper selection of an array for a particular design, to indicate the packaging available for that array, and to provide the designer with a better understanding of the capabilities of the Q14000 Series BiCMOS Logic Arrays.

Section 2 contains design rules specific to this array series. Interconnect rules and testing requirements are included in this section.

The macro summary and detailed macro specifications are presented in reference manual format in Section 6 with a rapid graphic reference provided via quicksheets in Section 7. Either a macro-conversion of an existing design, or the direct design of a circuit can be implemented using the available macros.

Volume 2 of this design manual is composed of the following sections:

- Section 1: Introduction

- Section 2: EWS-Specific Design Methodology

- Section 3: EWS Schematic Rules and Conventions

- Section 4: Vector Submission Rules and Guidelines

- Section 5: Design Validation

- Section 6: Design Submission

Section 7: MacroMatrix<sup>R</sup> Installation

- Section 8: MacroMatrix User's Guide

- Section 9: AMCC Glossary

- Section 10: Index

Volume 2, Section 2 of this design manual contains the Engineering-workstation (EWS) design methodology, covering both the EWS-specific operations and the AMCC MacroMatrix support software.

Section 8 contains the MacroMatrix User's Guide which details the Engineering Rules Check (AMCCERC, a.k.a., ERC) software checks and error messages and probable causes. It also includes the Vector Rules Check (AMCCVRC) user's guide. Section 9 contains the MacroMatrix Installation and Operations manual, which summarizes the EWS-specific commands required for operation of the AMCC support software.

The Design Validation document in Section 5 details the engineering rules checks that must be reviewed prior to design submission. It is the basic outline of the design review AMCC performs prior to circuit acceptance. Fill in or check off items as indicated and submit the entire document as part of the design submission package. Additional copies can be obtained from AMCC.

The Design Submission Document in Section 6 is to be completed and submitted along with the design submission package. Additional copies can be obtained from AMCC.

The following trademarks are recognized by AMCC throughout this design manual:

- TEGAS V General Electric Co.

- COPTR General Electric Co.

- LOGICIAN Daisy Systems Corp.

- GATEMASTER Daisy Systems Corp.

- Mentor Graphics

- MacroMatrix AMCC

- Tektronix/CAE Systems

- Valid Logic

### Q14000 SERIES DESCRIPTION

The AMCC Q14000 Series Logic Arrays provide an optimized systems approach to BiCMOS semi-custom applications. CMOS logic for low power is combined with bipolar drivers for high drive capability within each internal cell. Mixed-mode I/O is combined with an advanced, interactive CAD system-based design approach to provide a quick and cost-effective solution to discrete IC replacement. Manufacturing advantages gained from the use of the AMCC logic arrays include:

- Increased circuit density

- Increased system speed

- Reduced power

- Higher reliability

- Lower system cost

- Operation over both military and commercial temperature ranges

The AMCC Q14000 Series Logic Arrays Macro Library is supported on the Daisy, Mentor Graphics, Valid Logic and Tektronix/CAE Systems EWS. The designer can use any of these systems in conjunction with AMCC's MacroMatrix software package to perform schematic capture, Engineering Rules Checking (AMCCERC), simulation, automatic test pattern formatting (AMCCSIMFMT), AMCC Vector Rules Checking (AMCCVRC), Front-Annotation and Back-Annotation. Simulation, AMCCERC error checking, AMCCVRC rules checking, Front-Annotation and Back-Annotation are also supported on VAX/VMS systems with TEGAS 5.

The Q14000 Series arrays are BiCMOS arrays. They have the ability to externally interface to either Schottky TTL, ECL 10K or ECL 100K. ECL 10K or ECL 100K may be standard-reference or +5V reference ECL.

As an added feature, the Q14000 Series provides the ability to mix ECL 10K and TTL or ECL 100K and TTL on the same array. ECL 10K and ECL 100K outputs are also allowed on the same array, regardless of the ECL type used for input. For other combinations, please contact AMCC Marketing.

All of the interface options are realized through the choice of appropriate macros, and personalized with the metal masks only.

AMCC describes the density of its logic arrays in terms of equivalent gates (2-input NAND gates), which are a function of the density of the available macros and the number of cells available in any given array. The density of the Q14000 Series is described below.

| 1      | ABLE 1-2         |

|--------|------------------|

| ARR    | AY DENSITY       |

| Array  | Equivalent Gates |

|        |                  |

| Q9100B | 9072             |

| Q2100B | 2160             |

|        |                  |

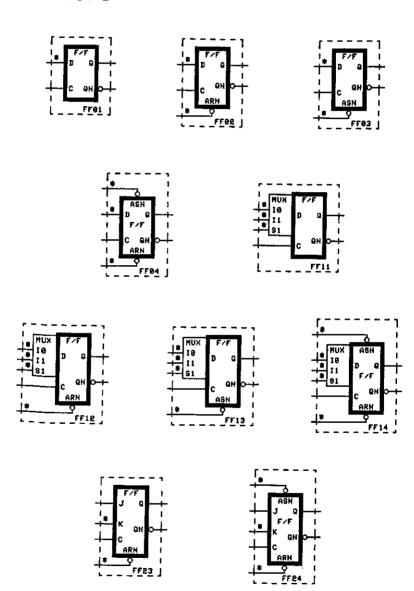

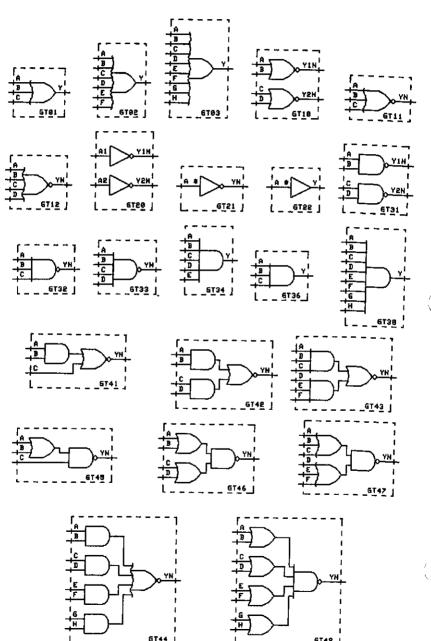

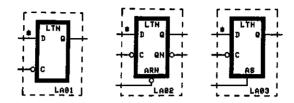

The arrays in the Q14000 Series share a common macro function library which contains a wide selection of fully characterized logic functions varying from SSI to MSI densities. The higher functionality macros have correspondingly higher equivalent gate densities.

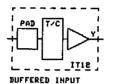

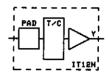

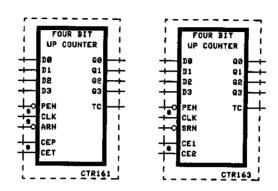

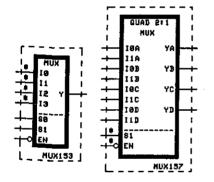

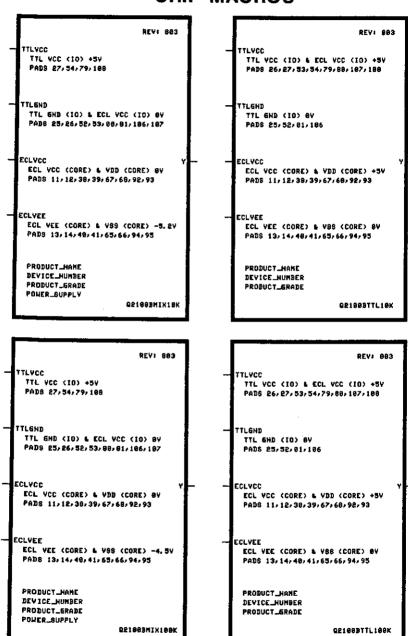

Examples of the basic logic functions include simple and complex gates, EXOR-nets, latches, decoders, MUXs, 4-bit counters, a 4-bit universal register, buffered input, high-speed ECL input, buffered and unbuffered output and ECL output macros which contain logic, buffers and output translation.

AMCC logic arrays are structured to allow the components spread across several cells to be interconnected into a single high-functionality MSI macro. These hard-wired MSI macros guarantee consistent and predetermined circuit performance. AMCC recommends that designers use the higher functionality MSI macros whenever possible.

Many interface macros in the Q14000 Series macro library have high-speed (H) options in addition to the standard (S) option of the macro. These macro options allow a designer to selectively program critical I/O paths with high-speed operation while implementing the remainder of the I/O in lower power standard-option macros.

### TYPICAL APPLICATIONS

Typical applications include high-speed computers, graphics, communications, test equipment and instrumentation. Designed to operate in the full MIL-SPEC temperature and voltage range, the Q14000 Series also has applications in radar, EW, avionics, guidance, flight simulation and other military systems.

### **FEATURES**

A summary of the features of the Q14000 Series includes:

- 9072 and 2160 equivalent gate versions

- 1.5-micron Bipolar/CMOS technology N-type epitaxial for both NPN oxide-isolated bipolar and CMOS

- 2-layer metal to customize base array

100% autoplace and autoroute with up to 95% logic cell utilization

- Extensive macro library, upwardly compatible with the Q3500 and Q1500 Series library

- System-level multiple-cell MSI macros

- Schottky TTL, low-power Schottky TTL, ECL 10K and ECL 100K I/O compatibility

- Standard-reference ECL or +5V referenced ECL

- Speed/power programmable I/O macros

- On-chip translators for mixed mode interface

- Both ECL 10K and ECL 100K outputs may appear on the same array

• Lower overall worst-case multipliers than CMOS

- Fast on-off chip delays

- Low fan-out degradation

- High internal noise immunity

- Unused cells do not dissipate power

- Internal core uses no DC current despite bipolar drivers

- Multiple power supply options available

- Fully voltage- and temperature-compensated internal logic

- Full MIL operating range (-55°C ambient to +125°C case, ±10% power supply)

- Wide selection of packaging

- Supported on engineering workstations:

- Daisy

- Valid Logic

- Mentor Graphics → Tektronix/CAE systems

- Supported on TEGAS 5

- Full CAD support, including post-autoroute, worst-case timing analysis

### **DESIGN INTERFACE AND SUPPORT**

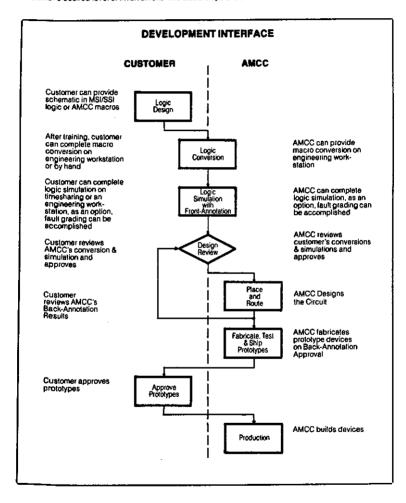

The AMCC circuit development interface has been structured to be highly flexible with respect to the customer's desired level of involvement. The basic steps are summarized below:

FIGURE 1-1

# Section 2: Design Methodology

|                                                     | , ,  |

|-----------------------------------------------------|------|

| Table of Contents                                   | 2-2  |

| Device Architecture                                 | 2-5  |

| Macro Configuration                                 | 2-5  |

| Interconnections and Routing                        | 2-8  |

| Basic Cells                                         |      |

| I/O Cells                                           | 2-9  |

| Overhead Circuitry                                  | 2-9  |

| Interface Options                                   | 2-10 |

| Interface Guidelines                                | 2-1] |

| Macro Summary                                       | 2-1] |

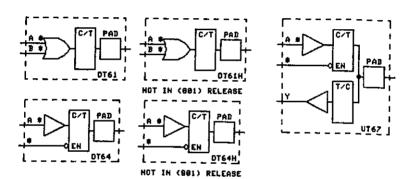

| I/O Macros                                          | 2-16 |

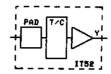

| TTL Input (ITxx Macros)                             | 2-16 |

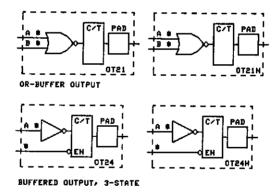

| TTL Output (OTxx Macros)                            | 2-17 |

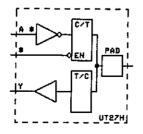

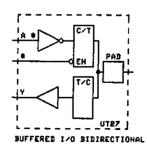

| Bidirectional TTL (UTxx Macros)                     | 2-17 |

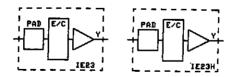

| ECL Input (IExx Macros)                             | 2-18 |

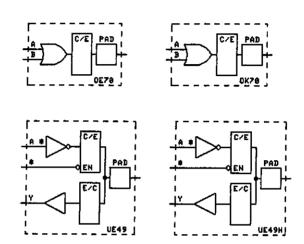

| ECL Output (OExx, OKxx Macros)                      | 2-18 |

| Bidirectional ECL (UExx, UKxx Macros)               | 2-19 |

| +5V Referenced ECL/TTL                              | 2-19 |

| Simultaneously Switching Macros                     | 2-19 |

| Alternative ECL Terminations                        |      |

| Power Busses                                        |      |

| Adding Extra TTL V <sub>CC</sub> - TTL GROUND Pairs | 2-20 |

| Adding Extra ECL V <sub>CC</sub> (I/O)              |      |

| Specifying Additional Power and Ground              |      |

| SWGROUP Parameter                                   | 2-22 |

| Characterizing the Array - The Chip Macros          |      |

| AMCCERC - Population                                |      |

| Total Array Pads                                    | 2-25 |

| AMCCERC Technology Check                            | 2-25 |

| Internal Fan-Out                                    |      |

(803)

DESTON METHODOLOGY

| Internal Cell Utilization             | 2-28 |

|---------------------------------------|------|

| Internal Pin Count                    | 2-29 |

| Q14000 Series Basic Design Rules and  |      |

| Guidelines                            | 2-30 |

| Power Bus Distribution and Decoupling | 2-33 |

| Testability                           | 2-35 |

| Structured Design                     | 2-35 |

| Testability Analysis                  | 2-35 |

| Functional Simulation                 | 2-36 |

| At-Speed Simulation                   | 2-37 |

| AC Tests Simulation                   | 2~37 |

| Design for Testability                | 2-38 |

| Design for Reliability                | 2-39 |

| Figure 2-1 Q9100B Die Plot                    | 2-6  |

|-----------------------------------------------|------|

| Figure 2-2 Q14000 Interface Guidelines        | 2-12 |

| Figure 2-3 Bidirectional TTL                  | 2-17 |

| Figure 2-4 Chip Macros; Power and Ground      | 2-24 |

|                                               |      |

|                                               |      |

| Table 2-1 Q14000 Series Cell Resource Summary | 2-5  |

| Table 2-2 I/O Resources                       | 2-7  |

| Table 2-3 Power Supply Options                | 2-10 |

| Table 2-4 I/O Macro Documentation Index       | 2-16 |

| Table 2-5 ECL Macro Selection                 | 2-19 |

| Table 2-6 Additional Power/Ground             | 2-21 |

| Table 2-7 Total Array Pads                    | 2-25 |

| Table 2-8 Derating Guidelines                 | 2-26 |

| Table 2-9 Maximum Internal Cell Utilization   | 2-28 |

| Table 2-10 Maximum Internal Pin Count         | 2-29 |

### DEVICE ARCHITECTURE

The AMCC logic arrays are formed from a customer specified design added to an AMCC pre-processed silicon base array. The base array for the Q14000 Series BiCMOS arrays is composed of two types of cells, I/O and Basic cells. Each cell consists of a number of uncommitted transistors and resistors.

| Q14000 SERIES                 | TABLE<br>CELL R |           | SUMMA        | RY          |

|-------------------------------|-----------------|-----------|--------------|-------------|

| Cell Type                     |                 | Qu<br>Q91 | antit<br>00B | у<br>Q2100В |

| Logic (Basic<br>Interface (I/ |                 | 22<br>16  | 68<br>0      | 540<br>80   |

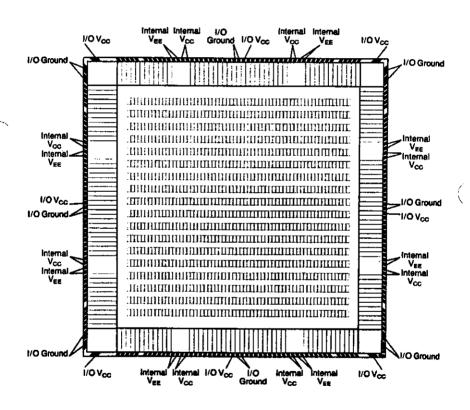

The basic cell layout of the arrays is demonstrated with the Q9100B, shown in Figure 2-1. Table 2-1 summarizes the internal cell resources and Table 2-2 summarizes the I/O resources for the Q14000 logic array series.

### MACRO CONFIGURATION

A customer design is described via schematics using the macros contained in the released library for the array series. Macros are individually configured in an array by interconnecting the components within a cell with the first layer metal to form the customer-selected macro functions. Macro placement is performed automatically by the AMCC proprietary CAD software.

### **Q9100 DIE LAYOUT**

FIGURE 2-1

| TABLE 2-2<br>I/O resources |                                         |        |        |  |  |

|----------------------------|-----------------------------------------|--------|--------|--|--|

| MODE                       | DESCRIPTION                             | Q9100B | Q2100B |  |  |

| TTL                        | I/O Cells                               | 160    | 80     |  |  |

| SYSTEM                     | v <sub>cc</sub> (+5v)                   | 32     | 16     |  |  |

|                            | GROUND                                  | 24     | 12     |  |  |

|                            | I/O Cells                               | 160    | 80     |  |  |

| System                     | V <sub>CC</sub> **                      | 40     | 20     |  |  |

| any                        | VEE *                                   | 16     |        |  |  |

|                            | I/O Cells                               | 160    | 80     |  |  |

| $\mathtt{TTLMIX}$          | V <sub>CC</sub> (+5V <sub>DC</sub> NOM) | 8      | 4      |  |  |

| and ECL                    | VEE *                                   | 16     | 8      |  |  |

|                            | TTL GROUND                              | 8      | 4      |  |  |

|                            | ECL V <sub>CC</sub> **                  | 24     | 12     |  |  |

| MIXED                      |                                         |        |        |  |  |

| +5V                        | I/O cells                               |        | 80     |  |  |

| System                     | V <sub>CC</sub> (+5V <sub>DC</sub> NOM) | 32     | 16     |  |  |

|                            | GROUND                                  | 24     | 12     |  |  |

<sup>\*</sup> V<sub>EE</sub> is -5.2V FOR STD-REF ECL 10K -4.5V FOR STD-REF ECL 100K 0V FOR +5V REF ECL 10K OR ECL 100K

<sup>\*\*</sup> V<sub>CC</sub> is 0V FOR STD-REF ECL 10K

0V FOR STD-REF ECL 100K

+5V FOR +5V REF ECL 10K OR ECL 100K

### INTERCONNECTIONS AND ROUTING

Interconnections between macros (routing) use both the first and second layers of metal, following specific routing tracks. Routing is performed automatically by AMCC proprietary CAD software. To allow for a high logic cell utilization and an optimum layout for high-speed logic designs, a liberal allocation of first metal vertical routing tracks and second metal horizontal routing tracks have been incorporated into the architecture for each array.

Additionally, the AMCC CAD software has been designed to automatically transform a logic design implemented in AMCC macros into an efficient high performance layout design. If there are sensitive timing and/or skew constraints, AMCC can optionally offer preplacement of the macros implementing these critical areas.

The customization of the array is performed by adding the 2-layer metal interconnect, representing the macros and their interconnection, to the base array.

### BASIC CELLS

The internal logic cells, called Basic cells, utilize both CMOS and bipolar devices. The internal logic is performed in CMOS while the bipolar device pairs provide necessary drive capability.

The Basic cells are organized to support high-level logic functions such as latches, multiplexors, decoders, etc. Simple and complex gates can also be made from these cells.

### I/O CELLS

The interface to the arrays is accomplished in the 100% bipolar input/output cells on the Q14000 Series Logic Arrays. The I/O cells are located around the perimeter of the array. For all arrays, ECL- and TTL-translators and most of the required buffers are included in the I/O cells for external interfacing to both ECL and TTL. Each individual I/O cell is configurable to be either TTL, ECL 100K or ECL 100K.

### OVERHEAD CIRCUITRY

In addition to the cells, each array contains overhead circuitry: bias generators, voltage references and voltage regulators. Overhead circuitry is predefined by AMCC.

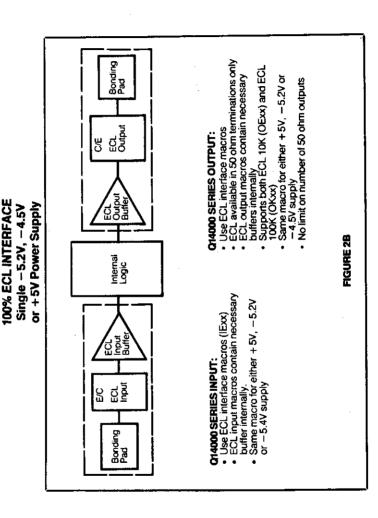

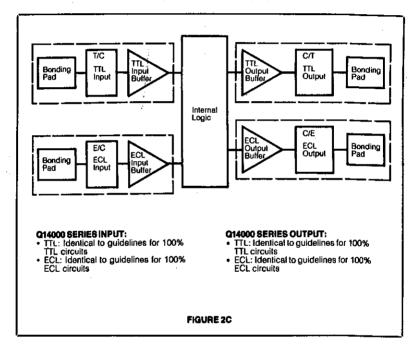

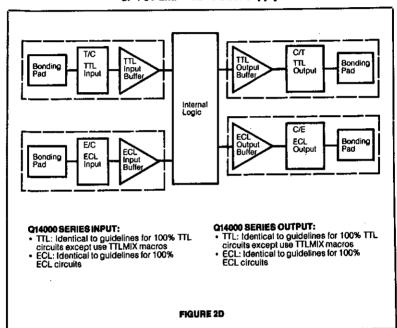

### INTERFACE OPTIONS

The array itself can be configured to be 100% TTL, 100% ECL 10K, 100% ECL 100K, TTL/ECL 10K or TTL/ECL 100K, with either dual power supplies or a single +5V supply available for either the 100% ECL or mixed mode I/O circuits. (See Table 2-3.) In addition, both ECL 10K and ECL 100K outputs may be used on any given array. Only one type of ECL is allowed for input.

TABLE 2-3

POWER SUPPLY OPTIONS\*

|               |      |   |        |      |          | ER SUPPLY<br>V +5V/-4 |            |

|---------------|------|---|--------|------|----------|-----------------------|------------|

| 100% TTL      | •    |   | -      | 1    | -        | -                     | 1          |

| 100% ECL 10K  | •    | • | •      | ı    | -        | -                     | - ı<br>ı ı |

| 100% ECL 100K | •    | • | •      | ı    | _        | -                     | ı          |

| ECL 10K/TTL   | •    | - | -      | ı    | •        | I •                   |            |

| ECL 100K/TTL  | •    | - |        | 1    | •        | l •                   | 1          |

| # ECT 10% can | bo o |   | st ECT | 1001 | 7 voltan | ag and                | _          |

<sup>\*</sup> ECL 10K can be operated at ECL 100K voltages and visa versa

### INTERFACE GUIDELINES

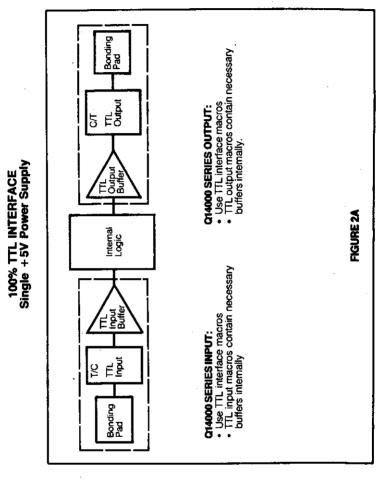

A summary of the interface guidelines for the four I/O modes of operation are shown in Figure 2-2. Most of the I/O macros for the Q14000 Series include buffer functions, to simplify I/O selection. The designer should review the I/O options to determine where these options would enhance the circuit efficiency.

### MACRO SUMMARY

Refer to the macro summary and index (Section 6) for a list of the macros available for the Q14000 Series Logic Arrays. The library and its summary sheets are for use during macro conversion or when creating a new design directly from the available functions. If other macro functions are desired, please consult AMCC.

The macro summary in Section 6 is divided into six segments: TTL Interface, TTLMIX Interface, ECL Interface, Basic Logic Macros, MSI Macros and Special macros. The macros are in alphabetical order within those sections.

# Q14000 SERIES INTERFACE MACRO GUIDELINES

Q14000 SERIES INTERFACE MACRO GUIDELINES (CONTINUED)

### Q14000 SERIES INTERFACE MACRO GUIDELINES (CONTINUED)

### MIXED ECL/TTL INTERFACE Single +5V Power Supply

### Q14000 SERIES INTERFACE MACRO GUIDELINES (CONTINUED)

### MIXED ECL/TTL INTERFACE + 5V and - 5.2V Power Supply or +5V and - 4.5V Power Supply

### I/O MACROS

Interface macros are documented in Sections 6-1, 6-2 and 6-3. All signals going on or off the chip require the use of an appropriate interface macro.

| I/O MAC | TABLE 2-4<br>RO DOCUMENTATION INDEX<br>Interface Macro Type |

|---------|-------------------------------------------------------------|

| 6-1     | TTL for 100% TTL                                            |

| 6-2     | TTL for ECL/TTL with +5V TTL for ECL/TTL,                   |

| 6-3     | dual power supplies ECL, any                                |

For +5V only circuits, the TTL macros are selected from the TTL section, Section 6-1. For dual power supply circuits, the TTL macros are selected from the TTLMIX section, Section 6-2. The ECL macros are selected from the ECL section, Section 6-3. The same ECL macros are available for use with standard reference voltage or for +5V reference voltage circuits.

### TTL INPUT (ITxx macros)

Q14000 Series TTL input macros contain input buffers. TTL level detection is performed in this input macro. For circuits with a single +5V power supply, the buffer provides the signal buffering required to drive internal circuits. For dual power supply circuits, the buffer also provides signal translation from TTL input levels to the internal CMOS signal level needed by the array, which operates with a negative power supply.

### TTL OUTPUT (OTxx macros)

The Q14000 Series arrays provide 20mA current sink, lmA current source capability. The TTL output is differentially driven by the buffered logic that is part of the TTL output macro.

The Q14000 Series arrays handle TTL totem-pole, open-collector and 3-stated output options. The 3-state output macro enable pin may be driven by any internal-level logic signal (the output of an input or internal logic macro). The signal driving the enable pin must be named on the schematic and must be listed in the simulation signal format.

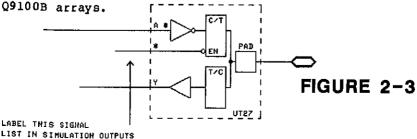

### BIDIRECTIONAL TTL (UTxx macros)

The Q14000 Series I/O cell supports bidirectional I/O. The input and output functions follow the same design methodology as the ITxx and OTxx macros. The bidirectional macro enable pin may be driven by any internal-level logic signal (the output of an input or internal logic macro). The signal driving the enable must be named on the schematic and must be listed in the simulation signal format.

Bidirectional macros are placed in specifically designed I/O cells, limited to 20 on the Q2100B and 40 on the

### ECL INPUT (IExx macros)

ECL input macros contain an RC compensation network and an input buffer. ECL inputs function in the same manner on circuits which have +5V referenced ECL input with a single +5V power supply.

### ECL OUTPUT (OExx, OKxx macros)

All ECL outputs require a buffer, and the buffer is included in the output macro. The Q14000 Series ECL output buffers drive 50 ohm ECL outputs.

ECL output macros are grouped by logic function in Section 6. A specific version of the macro (OExx or OKxx) is selected based on ECL type.

### SIMULTANEOUSLY SWITCHING MACROS

The inputs to an internal macro are considered to be switching simultaneously if they change within the macro propagation delay, i.e., one input changes while a previous input change is still propagating through the macro. For output macros, TTL outputs are considered to be simultaneously switching if they switch within 3ns of each other. ECL outputs are considered to be simultaneously switching if they switch within 2ns of each other.

TABLE 2-5

ECL MACRO SELECTION

|             |        |      |     |     |         |         | _    |

|-------------|--------|------|-----|-----|---------|---------|------|

| Q14000 Ser: | 5V REF | GND  | REF | į 4 | -5V REF | GND REF | <br> |

|             |        |      |     |     |         |         | ı    |

| Inputs      | IExx   | •    |     | ĺ   |         | IExx    | l    |

| OUTPUTS     | OExx   | I QE | кx  | ŀ   | OKxx    | OKxx    | 1    |

| Bi-direc.   | UExx   | UE   | к×  | 1   | UKxx    | ) UKxx  | 1    |

|             |        |      |     |     |         |         | _    |

### BIDIRECTIONAL ECL (UExx, UKxx macros)

The Q14000 Series I/O cell supports bidirectional ECL I/O. The input and output functions follow the same design methodology as the IExx and OExx/OKxx macros. The macro enable pin may be driven by any internal-level logic signal (the output of an input or internal logic macro). The signal driving the enable pin must be named on the schematic and must be listed in the simulation signal format.

Bidirectional macros are placed in specifically designed I/O cells, limited to 20 on the Q2100B and 40 on the Q9100B arrays.

### +5V REFERENCED ECL/TTL

AMCC offers the option of having ECL 10K or ECL 100K available with the use of a single +5V power supply. The ECL logic threshold levels are shifted, but retain their high-speed characteristics. This +5V referenced ECL mode allows the partitioning of a high-speed TTL design into multiple AMCC devices using a single +5V supply, while providing high-speed ECL I/O between the arrays on the same PC board and full system TTL compatibility.

### ALTERNATIVE ECL TERMINATIONS

The standard ECL termination is 50 ohms tied to  $V_{\rm TT}$ , where  $V_{\rm TT}$  = -2.0V for standard reference ECL. An alternative termination is 80 ohms to ground with 130 ohms to  $V_{\rm EE}$  where  $V_{\rm EE}$  = -5.2V. For other termination configurations, consult AMCC.

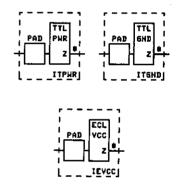

### **POWER BUSSES**

The power busses supporting the internal array are isolated from the busses supporting the peripheral I/O cells to minimize the effect of noise coupling between the core and the I/O. The TTL and the ECL ground busses are kept isolated on the chip.

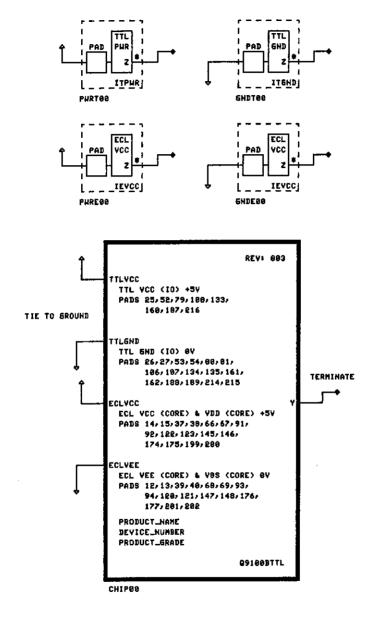

When necessary, there are macros available to provide extra TTL power (ITPWR), TTL ground (ITGND), and ECL power or ground (IEVCC), depending on the reference voltage.

ADDING EXTRA TTL V<sub>CC</sub> - TTL GROUND PAIRS (ITPWR-ITGND)

As a design guideline for 100% TTL circuits and for mixed mode ECL/TTL circuits, the designer should allocate a minimum of one additional TTL  $V_{\rm CC}$  pad and one TTL GROUND pad to any quadrant of the chip that has more than eight (8) simultaneously switching TTL outputs.

An additional pair is required for each additional eight (8) simultaneously switching outputs in that same quadrant. (See Table 2-6.)

# ADDING EXTRA ECL 10 VCC (IEVCC)

As a design guideline for any standard reference or +5V reference ECL circuit, the designer should allocate a minimum of one additional ECL VCC pad to any quadrant of the chip that has more than eight (8) simultaneously switching ECL outputs.

An additional ECL VCC (IEVCC) pad is required for each additional eight simultaneously switching ECL outputs in that same quadrant. (See Table 2-6.)

TABLE 2-6

ADDITIONAL POWER/GROUND

Q14000 SERIES

| # OF SIMULTANEOUSLY SWITCHING TTL OUTPUTS                    | ADD TTL V <sub>CC</sub> - TTL GROUND                      |

|--------------------------------------------------------------|-----------------------------------------------------------|

| PER QUADRANT                                                 | ADDED ITPWR - ITGND PAIRS                                 |

| 0 - 8<br>9 - 16<br>17 - 24<br>25 - 32*                       | 0<br>1 (2 pads)<br>2 (4 pads)<br>3 (6 pads)               |

| # OF SIMULTANEOUSLY<br>SWITCHING ECL OUTPUTS<br>PER QUADRANT | ADDED IEVCC                                               |

| 1 - 8<br>9 - 16<br>17 - 24<br>25 - 32<br>33 - 36*            | 0<br>1 (1 pad )<br>2 (2 pads)<br>3 (3 pads)<br>4 (4 pads) |

<sup>\*</sup> There is a MAXIMUM of 40 I/O cells per quadrant in the largest array (the Q9100B). For this array, the SSO limit in a quadrant for TTL is 32 TTL SSO + 6 power-ground pairs. For this array, the SSO limit in a quadrant for ECL is 36 ECL SSO + 4 ECL VCC pads.

#### SPECIFYING ADDITIONAL POWER AND GROUND

when additional power and ground pads are desired, the power macros, ITPWR or IEVCC, and the ground macros, IEVCC or ITGND, are placed on the schematic in the quantity desired. IEVCC will be considered a power pad for +5V REF ECL circuits and a GROUND pad for STD REF ECL circuits.

The added power and ground macros each occupy one I/O cell and use its pad. Added ground and power pads <u>must be</u> <u>interspersed</u> with the simultaneously switching signals.

Inclusion of the requirements for extra power and ground is part of the required design submission documentation.

#### SWGROUP PARAMETER

When the added power and ground is for simultaneously switching circuits, use the macro parameter SWGROUP to tag these macros to the group to which they belong. The ERCs cannot issue error or warning messages on insufficient power or ground if the parameter is not used.

Note: The current AMCCERC algorithm is conservative when the number of simultaneously switching outputs exceeds what can be placed in a single quadrant of the array.

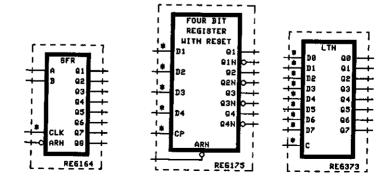

#### CHARACTERIZING THE ARRAY - THE CHIP MACROS

The AMCC EWS schematic convention for the specification of the array and its I/O mode, power supply, product grade, and circuit identification (MILitary or COMmercial) is through the use of a CHIP MACRO. Note that the chip macro POWER\_SUPPLY parameter allows the user to specify -5.2V, -4.5V or +5V for ECL circuits. The chip macros carry array-specific information used by AMCC MacroMatrix software in processing the design.

Refer to <u>EWS Schematic Rules and Guidelines</u> (Section 3 in Volume II) for placement and hook-up procedures. Volume I, Section 6-6 also documents the chip macros and their parameters.

The chip macros each carry the pads designated for use by the fixed power  $\langle V_{CC} \rangle$  and ground  $\langle V_{EE} \rangle$  pads required for that particular array and the specified I/O mode. Any power and ground pads added by the user are in addition to the fixed power and ground requirements.

Signals cannot be placed on the pads designated as being fixed power or ground pads. All fixed power and ground pads must be used. Fixed power and ground pads provide the minimum number of power and grounds for the array.

CHIP-POWER/GROUND

FIGURE 2-4

#### AMCCERC - POPULATION

#### TOTAL ARRAY PADS

The AMCC MacroMatrix Population ERC check will correctly reflect the cell count and the total pad count for the design independent of the package selected. The population ERC will report this number as the number of "external pins" used by a circuit, the sum of all fixed power and ground, all added power and ground and all interface signals. The total pad count for the design is used in determining package selection. The final number of package pins may be less-than, equal-to or greater-than the total number of array pads used by the design.

TABLE 2-7

TOTAL PADS

| ARRAY  | FIXED        | SIGNAL | TOTAL    |

|--------|--------------|--------|----------|

|        | POWER-GROUND | I/O    | EXTERNAL |

|        | PADS         | PADS   | PADS     |

| Q9100B | 56           | 160    | 216      |

| Q2100B | 28           | 80     | 108      |

#### AMCCERC TECHNOLOGY CHECK

The AMCC MacroMatrix ERC technology ERC report will list errors due to improper selection of macros based on the I/O mode selected via the chip macro.

#### INTERNAL FAN-OUT

Each internal macro output pin is specified to drive a maximum fan-out load. Maximum fan-out limits are specified for individual macros in the macro documentation in Section 6. The fan-out ERC checks for excessive fan-out loading.

#### DERATING FAN-OUT LIMITS

For clock or distortion-sensitive paths, at speeds up to 100MHz, the maximum fan-out for each macro output pin in the path must be derated by 20%. For clock paths at speeds equal to or greater than 100MHz, the maximum fan-out should be derated by 40%. The fan-out ERC will check for a derated fan-out load limit if the FOD net parameter has been used. AMCC requires the use of the FOD parameter on all clock nets.

TABLE 2-8

DERATING GUIDELINE

| OPERATING            | DERATE     | BY: | FOD VALUE |

|----------------------|------------|-----|-----------|

| < 100MHz<br>≥ 100MHz | 20%<br>40% |     | 20<br>40  |

#### STATIC SIGNALS

When an <u>internal</u> macro has an unused pin or it is desired to tie an internal macro input pin to "l" or to "0", the pin is tied to global VSS ("0") or VDD ("l"), not to global GROUND.

When an <u>output</u> or <u>bidirectional</u> macro has an unused input pin, the pin is tied to global GROUND and not to VSS or VDD. Global GROUND is a logic zero. To tie one of these pins to logic "l", they must be driven by a macro.

VDD and VSS are connected to the internal VDD and VSS busses but are not counted in the internal pin count. Global GROUND is not connected to anything, i.e., it is allowed to float. It is not counted in the internal pin count.

To help the designer, the AMCC MacroMatrix ERC Hook-up check will detect global GROUND, VSS and VDD improper interconnect.

#### INTERNAL CELL UTILIZATION

To insure routability, the recommended maximum internal cell utilization (cell population) for arrays in the Q14000 Series is 95%. Starting designs should target a 70% internal cell utilization to allow for the typical 20% design expansion during debug, re-design, enhancement, and testing logic additions. Designs in excess of 95% internal cell utilization for these arrays are considered risky if their internal pin count also exceeds recommended limits.

Compute internal cell utilization by first summing the number of L cells used by the circuit, and then by dividing that sum by the number of L cells available for the particular array.

TABLE 2-9

RECOMMENDED MAXIMUM

INTERNAL CELL UTILIZATION

L CELLS

| ARRAY  | 8  |

|--------|----|

|        |    |

| Q9100B | 95 |

| 02100B | 95 |

|        |    |

AMCC MacroMatrix ERC software computes the internal cell utilization. The software generates an error if cell utilization exceeds recommended limits or exceeds 100%.

#### INTERNAL PIN COUNT

The internal pin count is another measure of the routability of a circuit on a given array.

- Prior to schematic capture, the internal routable pin count should be estimated and used to determine the required array.

- After capture, the AMCC MacroMatrix ERC software provides a detailed report on the internal pin count of the circuit. For a captured circuit, refer to the limits in Table 2-10.

TABLE 2-10

MAXIMUM INTERNAL PIN COUNT

I/O AND L CELLS

| ARRAY  | LIMIT |  |  |

|--------|-------|--|--|

|        |       |  |  |

| 09100B | 8000  |  |  |

| 02100B | 2200  |  |  |

|        |       |  |  |

- A circuit with an actual internal pin count that is less than the limit is routable.

- ullet A circuit with an actual pin count that is 1-10% over the limit is considered risky (may have problems).

- A circuit with an actual pin count of 11-18% over the limit is considered very risky and may not successfully route.

- A circuit with an actual pin count of 18% or more over the limit is considered unroutable and a redesign is required if a larger array cannot be used.

#### 014000 SERIES BASIC DESIGN RULES AND GUIDELINES

Once the macros have been selected, and the basic circuit defined, the designer should review the circuit prior to submission to AMCC to verify that basic design rules have not been violated. Some of these rules and design checks are listed below.

Guidelines are suggestions to help ensure first-design success; rules are design requirements that cannot be violated. For further information, refer to the Design Submission and Design Validation documents, Section 6 and Section 5 of Volume II of this design manual.

- Fan-out no macro drives more than its rating

- Fan-out derating critical clock or distortion sensitive paths have derated clock loading: 20% up to 100MHz; 40% for ≥ 100MHz. Use the FOD parameter to allow ERC checking.

- Fan-out no macro output pin is to drive more than one input pin of a gate within a macro. Driving multiple inputs of a gate from the same source results in loss of noise immunity.

- Fan-out do not derate 3-state enable drivers.

- Fan-in any macro with an asterisk on an input pin has been checked for fan-in > 1.

- Pin-restrictions any macro with an asterisk has been cross-checked to be certain that it is connected to or driven from a legal macro connection.

- Unused macro input pins INTERFACE MACROS

EWS convention is to ground any unused inputs

unless the macro documentation indicates

that a pin cannot be grounded. (Grounded signals

assume low level logic and physically float.)

- Unused macro input pins INTERNAL MACROS EWS convention and design requirements dictate that unused internal macro input pins be tied to VDD or VSS.

- Pin connections Make certain that input and output pins are properly connected, including PAD connections.

- Bidirectional signals Be certain that bidirectional macro pins have been connected to a bidirectional connector (EWS convention). Refer to Volume II, Section 7 for additional information.

- Grounded output pins These are not allowed.

- Terminated input pins These are not allowed.

- Macro type Check that the proper TTL I/O macros were chosen based on the circuit type.

- Macro type Check that the proper ECL versions of the ECL macros were chosen based on the circuit type.

- Signal names Check that all connections intra-page, inter-page, off-chip and 3-state and bidirectional enables - have been properly named. Refer to Volume II, Section 3 for naming conventions and rules.

- Cell utilization Do not violate the internal cell utilization limit without AMCC approval.

- Internal pin count Do not exceed the array limit and supply AMCC with a total internal pin count.

- Additional power and ground Provide additional power and ground pins as needed by using the ITPWR, ITGND and IEVCC macros on the schematic. Use the SWGROUP macro parameter to allow the simultaneously switching output ERC check.

- When leaded chip carriers are to be used, care should be taken to supply sufficient ground pins to allow separation of any signals where crosstalk may be of concern, e.g., between input and output signals. Spare pins should be grounded.

- Total PAD count Do not exceed the maximum pad count limit for the array. ITGND, IEVCC, and ITPWR macros use cells and pads and are counted.

- Power Compute the maximum worst case power.

Combine the power dissipation of the interface macros with the power computed for the internal macros. Include any ECL static output power.

- Packaging Verify that the package selected is appropriate for the environment and junction temperature (compute based on power).

- Critical paths Compute and clearly identify the critical paths.

- Generate and include reports on macro occurrence, current and power; fan-out; pin count; etc. as indicated in the Design Submission and Design Validation documents. (AMCC MacroMatrix ERC software generates most of these reports.)

Refer to Section 8, Volume II.

- Use a chip macro to characterize the circuit as to array, ECL type and power supply. Follow the rules in AMCC EWS Schematic Rules and Conventions. Refer to Section 3, Volume II.

- Complete simulation documentation must be submitted with the design, including source files. Refer to the Design Submission and Design Validation documents.

- For guidance in constructing simulation vectors, refer to the AMCC document:

Vector Submission Rules and Guidelines.

Refer to Section 4, Volume II.

#### POWER BUS DISTRIBUTION AND DECOUPLING

Optimal Power Bus Distribution and Decoupling is dependent on a number of interactive device and system variables, including the package design used, the number of simultaneous switching outputs on the device, output loading, the amount of switching noise contributed by other system components, the number of power busses and the design of the system and module power distribution.

AMCC recommends the use of multi-layer PC boards that provide dedicated low impedence power and ground planes. Besides maintaining a constant characteristic impedence for transmission lines, the planes provide for a low impedence return path to the ECL or TTL circuitry and act as an electromagnetic shield for the signal lines. The distributed capacitance will also improve noise margins by minimizing "ground bounce" and crosstalk.

The 2-layer PC boards, on the other hand, may require successive approximations to optimize the system noise margins and reduce external noise from being fed back into the chip through the power and ground pins. This approach should only be attempted in lower performance systems.

The I/O ECL  $V_{\rm CC}$  and the Internal  $V_{\rm CC}$  package pins should be tied together as close to the chip as possible, using good high frequency practices. When mixed I/O is combined with multiple power busses, the TTL GND and ECL  $V_{\rm CC}$  (OV) can be tied directly together at the chip on multi-layer boards.

For 2-sided boards, the location will be system dependent and may require some experimentation. The primary considerations are the amount of simultaneous switching, the signal/ground pin ratio and the isolation between the TTL and ECL signal lines (and return paths).

Low frequency (bulk) decoupling is generally provided in the range of 0.5 to 2.0 uf/WATT, while high frequency by-passing should be 100 to 1,000 pF/quadrant. The by-pass capacitors are generally placed as close to the chip as possible using high frequency techniques to minimize the inductance in the leads, traces, feed-throughs and components.

The AMCC Q14000 performance boards use a luf tantalum capacitor in parallel with a 470pf ceramic chip capacitor for each of the Internal  $V_{\rm EE}/V_{\rm CC}$  pairs. This same combination is used for any  $V_{\rm CC}$  or additional  $V_{\rm CC}$  package pins with excellent results.

#### TESTABILITY

Concepts of testing and testability must be considered from the beginning of any circuit design. AMCC encourages: (1) the use of testability techniques in circuit design; (2) the use of testability analysis early in the design process so that testability problems can be corrected by design; (3) the use of fault grading to assess test vector fault coverage; and (4) an understanding of the capabilities of today's advanced test equipment in the development of semi-custom circuits.

#### STRUCTURED DESIGN

Structured approaches to ensure circuit testability such as LSSD, Scan Path and BILBO are generally driven by an overall system philosophy to testing. While AMCC does not promote one structured technique over another, other measures during design can improve circuit testability. AMCC does promote the use of overall structured design procedures, including functional modularity, bus architectures and clear documentation.

#### TESTABILITY ANALYSIS

All testability measures have one common goal: to enhance controllability and observability of the circuit. It is a grade on the logic design itself. Controllability is a measure of the ease in setting a particular node to a logic level of zero or one, while observability determines the ease of propagating the node's state to one or more primary outputs.

After a netlist has been created and logic simulation has verified correct functional performance, testability can be verified by running testability analysis programs such as DTA (DAISY) or COPTR (TEGAS).

#### FUNCTIONAL SIMULATION

The object of functional testing is to detect a single SAl or SAO fault in the circuit if one exists. This ideally requires sufficient vectors to "cover" all possible fault locations. The percent of coverage is the fault grade of the vector set. To this end, one approach is to cycle all inputs and outputs through 1-0 and 0-1 transitions as a first check after initialization. (This should cycle all internal nodes as well.) This 2<sup>n</sup> (n = number of inputs) brute force approach is not necessary. Minimum vector test sets and minimum vector test sequences will cover 100% of all observable faults.

Functional simulation vector fault-grading can be performed using the TEGAS simulator. Fault-grading is used to verify that the simulation bit vectors sufficiently exercise nodes within the circuit to assure that the outgoing product matches the customer specification. Insufficient fault coverage as determined in a fault grading run may require the addition of vectors to the set developed to evaluate logical functionality.

AMCC recommends the creation of a sufficient number of vectors to achieve a fault coverage of 90% or higher, and is prepared to perform the fault grading task upon request.

For guidelines in performing functional simulation, refer to <u>Vector Submission Rules and Guidelines</u> in Section 4, Volume II of this design manual.

AMCCVRC Vector Rules Checker must be run against the AMCCSIMFMT (AMCC Simulation Format) maximum worst-case sampled simulation output file.

#### AT-SPEED SIMULATION

In addition to functional simulation, the customer must perform an at-speed simulation and timing analysis for all critical (i.e., timing-sensitive) paths in the circuit. Refer to the above referenced document.

#### AC TESTS SIMULATION

AC path propagation delay tests require simulation vectors to initialize the circuit path to be measured and to support the measurement of the path. Provided the start and stop addresses are clearly documented, all AC tests may be grouped in one simulation file. Each AC test path must be clearly documented. A test path is defined as a single input to a single output. Refer to (708 REV A) of the previously referenced document.

If the path propagation delay to be measured is less than 10ns typical, consult AMCC.

#### DESIGN FOR TESTABILITY

Some specific design suggestions for improved circuit testability are:

- Become familiar with the macro library <u>BEFORE</u> beginning the macro conversion or design.

- Use synchronous rather than asynchronous circuits whenever possible - functional tests are synchronous.

- Partition the design (use structured design techniques) into smaller, testable sections, usually along a functional boundary.

- Use degating logic to isolate modules for test.

- · Use modular architecture, bus structures.

- Break up long counters (>8).

- Don't bury states.

- Use transparent latches instead of flip/flops where possible and use I/O latches instead of flip/flops.

- Use macros, especially flips/flops and latches, with RESET or SET controls where possible to simplify initialization.

- Avoid feedback loops.

- If unavoidable, provide a means to break up feedback loops during test (degating, enables).

- Avoid redundant logic minimize: or add test points to unmask masked faults.

- Avoid derived clocks they complicate testing.

- Design in test points, especially in sequential logic. Add test points to improve controllability and observability. Perform testability analysis.

- If I/O pins are limited, use demultiplexors to control and multiplexors to observe internal nodes with otherwise poor observability (buried states).

- Any 3-state enable control signal that is internally generated must be externally observable, and should be externally controllable during test.

- Add parity trees for error detection. Or use Scan Path Design to simplify test sequence generation or use Level Sensitive Scan Design to simplify test sequence generation.

Keep test generation in mind while designing the circuit.

#### DESIGN FOR RELIABILITY

Some specific design suggestions for improved circuit reliability are:

- Become familiar with the macro library <a href="BEFORE">BEFORE</a> beginning the macro conversion or design.

- Be aware of "glitch" circuits. Do not use potential glitch circuits to drive clock inputs.

- Avoid one-shot pulse generators.

- Avoid gated and derived clocks.

- Avoid race and hazard conditions. (PRINT\_ON\_CHANGE files can help identify these.) These are generated by having a signal follow two or more paths to a common circuit element (a.k.a. reconvergent fan-out.)

- Avoid feedback loops.

- If unavoidable, provide a means to break up feedback loops during test (using degating, enables).

- Avoid feedback paths between registers. If present, compute the worst-case set-up and hold times and verify operation. (Feedback from the ECL output macros must be handled with care if used to input to internal latches and flip/flops.)

- Add sufficient GROUND for the number of simultaneously switching outputs and distribute among these outputs (similar to distributed ground in a ribbon cable). Add additional extra ground if there are extra I/O pins available.

- $\bullet$  Add extra  $V_{CC}$  as needed for the number of simultaneously switching outputs.

- Properly derate fan-out on all distortion-sensitive paths and all clock paths. Keep clock path loading balanced.

# Section 3: Timing Analysis

| Table of contents                              | 3-2  |

|------------------------------------------------|------|

| Computing Propagation Delay                    | 3-3  |

| Preliminary Computation - Prior to Capture     |      |

| Front-Annotation - After Capture               |      |

| Back-Annotation - After Layout                 |      |

| Typical Individual Macro Propagation Delay     |      |

| Intrinsic Set-up and Hold Times                |      |

| Recovery Time                                  |      |

| Asymmetry in the Worst-Case Path               |      |

| Effect of Loading on Output Macro Delays       |      |

| Computing the Loading Delay for a Net -        |      |

| Front Annotation                               | 3-8  |

| Computing Lnet                                 | 3-9  |

| Computing L <sub>fo</sub>                      | 3-11 |

| Worst-Case Delay Multiplication Factors        |      |

| Selecting the Correct Timing Multiplier        |      |

| Minimum Propagation Delay                      |      |

| Result                                         |      |

| Asymmetry in the Worst-Case Path               |      |

| Internal Signal Tracking                       |      |

| Signal Balancing; Distortion Minimization      |      |

| Maximum Operating Frequency                    |      |

| Front-Annotation Load Units                    |      |

| Back-Annotation Load Units                     | 3-19 |

|                                                |      |

| Table 3-1 Ouput Loading Delays                 |      |

| Table 3-2 k Factors - Q14000                   | 3-9  |

| Table 3-3 Front-Annotation Statistical         |      |

| Wire Loads (L <sub>net</sub> )                 | 3-10 |

|                                                | 3-12 |

| Table 3-5 Application Rules for the Worst-Case |      |

| Delay Multiplier                               |      |

| Table 3-6 Maximum Operating Frequency          |      |

| Table 3-7 Front-Annotation Load Units          | 3-19 |

| Table 3-8 Back-Annotation Load Units           | 3-19 |

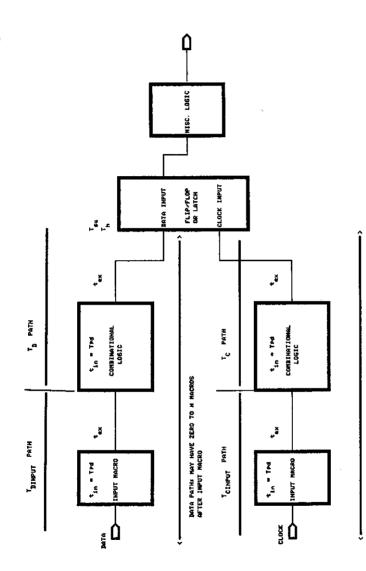

#### COMPUTING PROPAGATION DELAY

The macros selected, the options of those macros, the loading on the macros, and the final layout of the circuit are all factors in the propagation delay of any path. The loading may be the interconnect capacitance or the external load capacitance due to system loading and package pin capacitance.

There are two approaches that can be used to compute propagation delay: Front-Annotation, where a <u>statistical</u> <u>estimate</u> of metal delays based on net sizes is used; and Back-Annotation, where the <u>actual</u> metal delay is used in the computation.

#### • PRELIMINARY COMPUTATION - PRIOR TO CAPTURE

The path propagation delays can be <u>estimated</u> using the statistical wire delay tables  $(L_{\text{net}})$ , fan-out loading  $(L_{\text{fo}})$  and the appropriate k-factors (k) for the macros chosen. The equation for the typical extrinsic (load) delay for a single net is shown below and discussed in detail on the following pages.

$$t_{ex} = k * (L_{fo} + L_{net})$$

The sum of all typical intrinsic macro delays in the path  $(t_{in};$  specified as Tpd in the macro documentation) and all extrinsic loading  $(t_{ex})$  is then multiplied by the proper ANNOTATED worst-case timing multiplication factor.

#### • FRONT-ANNOTATION - AFTER CAPTURE

After schematic capture, Front-Annotation software is available to provide the designer with a file of rising and falling edge delays per net (expressed as NOM, MIN and MAX). By incorporating this file into the simulation database, the designer can obtain a statistical estimate of circuit performance.

#### BACK-ANNOTATION - AFTER LAYOUT

The most accurate method of computing a circuit propagation delay requires that the circuit be completed through layout. Back-annotation software adds the actual metal delay and fan-out delays into the path. Back-annotation must be run and accepted as final prior to the generation of the actual silicon arrays. The Back-Annotation program provides a file which includes the ACTUAL metal delays in a net.

AMCC guarantees that the silicon will match (will not be slower than) the results of the Back-Annotation.

#### • TYPICAL INDIVIDUAL MACRO PROPAGATION DELAY

AMCC macro documentation specifies <u>typical</u>, unloaded macro path propagation delays (Tpd) for each path through a macro. Some macro specifications include a different delay for a rising edge (Tpd-+) than for a falling edge (Tpd+-). Three-state macros have specifications for high-Z representative switching delays  $T_{\rm PHZ}$ ,  $T_{\rm PZL}$  and  $T_{\rm PLZ}$ .

(803)

The actual macro path delay will be a function of: state of the input data (low data may have different set-up and hold times than high data); multiple inputs changing state (e.g., when several OR/NOR inputs change simultaneously on an internal macro, the delay increases).

To account for some of these path delay variations, the AMCC macro specifications have been expanded to show the model behavior in more detail. The specifications are interpreted as follows:

Non-inverting:

Tpd++ rising edge input; rising edge output

Tpd-- falling edge input; falling edge output

Inverting:

Tpd+- rising edge input; falling edge output

Tpd-+ falling edge input; rising edge output

All AMCC EWS <u>simulation models</u> are accurate to within lops (two decimal place accuracy when measured in ns).

AMCC macro specifications, as documented in the Design Guides and Design Manuals for the individual array series, show the typical propagation delay for a path through a macro for nearly all of the possible conditions. Multiplexer specifications are simplified.

#### . INTRINSIC SET-UP AND HOLD TIMES

The intrinsic set-up and hold times for the latches, flip/flops and MSI macros that include one or more of these types of devices, are specified in the macro summary in Section 6. The parameters represent the behavior of the macro as observed at its input and output nodes. Set-up time (Tsu) is the time that a signal must be stable prior to the active clock edge. Hold time (Th) is the time that a signal must be held after the active clock edge.

#### RECOVERY TIME

Recovery time (Trec) is specified for any latch or flop/flop which has a set or reset. It is the length of time that a reset/set signal has to have been inactive prior to an active clock edge. Clocking within the recovery time period will result in unpredictable behavior.

Note: Set-up time, hold time, recovery time and minimum pulse width are all specified as <u>typical</u> values and must be multiplied by the appropriate worst-case delay multiplication factor.

#### • EFFECT OF LOADING ON OUTPUT MACRO DELAYS

For output macros, Tpd is specified for a no load. The actual capacitive load driven will be the sum of the system load and the package pin capacitance. The capacitive load is converted to ns using the constants in Table 3-1. For TTL or ECL output loads up to but less than 100pf, use Table 3-1. For TTL or ECL output loads over 100pf, consult AMCC.

|        | TABLE    | 3-1      |   |

|--------|----------|----------|---|

| OUTPUT | LOADIN   | G DELAYS | , |

| CAPAC  | CITIVE . | LOADING  |   |

|        |          |          |   |

| TTL | 55ps/pf            |

|-----|--------------------|

| ECL | 55ps/pf<br>45ps/pf |

|     |                    |

The delay adjustment values for both TTL and ECL output capacitive loading are <u>typical</u> and must be multiplied by the worst-case multiplier for the selected operating conditions, therefore, at this step, the nominal case capacitive load delay should be added to the nominal path propagation delay.

# • COMPUTING THE LOADING DELAY FOR A NET - FRONT ANNOTATION

The method for manual computation of the effect of load units on the propagation path is:

For each net:

$$t_{ex} = k * (L_{fo} + L_{net})$$

L<sub>fo</sub> = the sum of the electrical fan-out loads

in a net. (Pins with a fan-in of 2

count as 2 electrical loads)

Lnet = the estimated metal delay from Table 3-3, indexed by the sum of the number of pins in the net minus 1 (i.e., index by [net size - 1]) (Pins with a fan-in of 2 count as 1 physical load)

TABLE 3-2 TYPICAL & FACTORS - Q14000 \* ns/LU INTERNAL MACROS: 0.025 - 0.045S-option 0.025 - 0.045k down S-option INTERFACE (I/O) MACROS: S-option 0.025 S-option 0.030 k<sub>down</sub> 0.025 H-option k down H-option 0.030 \* Refer to Section 6 for the

\* Refer to Section 6 for the k-factors for a specific macro.

### • COMPUTING Lnet

Compute the statistical metal estimate by counting the physical pins in the net (driving or source pins and destination pins), subtracting one (1), and using this number as the index to the following table. The number listed under a specific array is the estimate for the load units due to metal in the net.

# TABLE 3-3 FRONT-ANNOTATION Q14000 SERIES STATISTICAL WIRE LOADS

net

| INDEX<br>1-30                                                              | !                                                                                              |                                                                             | INDEX<br>31-60                                                                               |                                                                                        |                                                                                                            |

|----------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|

| PINS<br>  -1                                                               | -                                                                                              |                                                                             | PINS<br>  -1                                                                                 | Q2100B                                                                                 | і<br>І <b>Q9</b> 100в                                                                                      |

| 1<br>  2<br>  3<br>  4<br>  5<br>  6<br>  7<br>  8<br>  9                  | 1.00<br>1.58<br>2.06<br>2.50<br>2.50<br>2.89<br>3.26<br>3.61<br>3.94<br>4.26<br>4.57           | 3.17   4.11   5.02   5.92   6.80   7.67   8.53                              | 31<br>32<br>33<br>34<br>35<br>36<br>37<br>37<br>38<br>39<br>40                               | 9.64<br>9.85<br>10.05<br>10.25<br>10.45<br>10.65<br>10.84<br>11.03<br>11.22            | 1 25.95<br>1 26.70<br>1 27.45<br>1 28.20<br>1 28.94<br>1 29.69<br>1 30.43<br>1 31.17<br>1 31.90<br>1 32.64 |

| 11<br>  12<br>  13<br>  14<br>  15<br>  16<br>  17<br>  18<br>  19         | 4.87<br>  5.16<br>  5.44<br>  5.71<br>  5.97<br>  6.23<br>  6.49<br>  6.74<br>  6.98<br>  7.22 | 11.04     11.87     12.69     13.50     14.31     15.11     15.91     16.70 | 41  <br>  42  <br>  43  <br>  45  <br>  45  <br>  46  <br>  47  <br>  48  <br>  49  <br>  50 | 11.60<br>11.79<br>11.97<br>12.15<br>12.33<br>12.51<br>12.69<br>12.87<br>13.05<br>13.22 | 33.37   34.10   34.83   35.56   36.29   37.01   37.74   38.46   39.18   39.90                              |

| 21<br>  22<br>  23<br>  24<br>  25<br>  26<br>  27<br>  28<br>  29<br>  30 | 7.46<br>  7.69<br>  7.92<br>  8.15<br>  8.37<br>  8.59<br>  8.80<br>  9.02<br>  9.23<br>  9.44 | 19.06   19.84   20.61   21.38   22.15   22.91   23.68   24.44               | 51  <br>  52  <br>  53  <br>  54  <br>  55  <br>  56  <br>  57  <br>  58  <br>  59           | 13.40<br>13.57<br>13.74<br>13.91<br>14.08<br>14.25<br>14.42<br>14.58<br>14.75<br>14.91 | 40.62  <br>41.33  <br>42.05  <br>42.76  <br>43.47  <br>44.18  <br>44.89  <br>45.60  <br>46.01  <br>47.01   |

#### . COMPUTING LEO

Compute L<sub>fo</sub> by adding the sum of the <u>electrical load</u> of all loads driven. If a destination pin has a fan-in of 2, it counts as two electrical loads and as one physical pin. A destination may appear to have two physical loads internal to the macro. In these cases, the macro documentation will clearly identify the fan-in load represented by that pin. Physical fan-out internal to the macro does not affect the physical pin count.

#### WORST-CASE DELAY MULTIPLICATION FACTORS

Once the sum of all of the intrinsic and extrinsic propagation delays in a path or path segment is computed and adjusted for any external high-capacitive loading (system load and package pin capacitance), then the result must be multiplied to obtain the worst-case delay as follows:

Tpd typical \* M.F. = Tpd worst-case

Multiplication factors are shown in Table 3-4. The worst-case multipliers take into account the following:

- Process variations

- Temperature variations

- Voltage variations

- Signal skew

TABLE 3-4

WORST-CASE DELAY MULTIPLICATION FACTORS

WORST-CASE MULTIPLIERS FOR FRONT- AND BACK-ANNOTATION

WCM

| ,     |              | HO!!                 | in:             | TERFACE              |                | INTERNAL             |                |

|-------|--------------|----------------------|-----------------|----------------------|----------------|----------------------|----------------|

| 1     | MINIMUM      | min.<br>typ.<br>max. | <br> <br>       | 0.70<br>0.78<br>0.86 | <br> <br> <br> | 0.70<br>0.78<br>0.86 | <br> <br> <br> |

|       | NOMINAL      | min.<br>typ.<br>max. | <br> <br> <br>  | 0.90<br>1.00<br>1.10 | ]<br>t         | 0.90<br>1.00<br>1.10 |                |

| 1     | COMMERCIAL** | min.<br>typ.<br>max. | ]<br> <br> <br> | 1.11<br>1.23<br>1.35 | ]<br> <br>     | 1.27<br>1.41<br>1.55 | 1<br>1<br>1    |

| 11111 | MILITARY***  | min.<br>typ.<br>max. | !               | 1.19<br>1.32<br>1.45 | 1              | 1.59<br>1.77<br>1.95 | <u> </u>       |

\*\* T<sub>j</sub> 130° \*\*\* T<sub>j</sub> 150°

## TABLE 3-5 APPLICATION RULES FOR THE WORST-CASE DELAY MULTIPLIER

- Set-up time, hold time, recovery time and minimum pulse width are multiplied by a worst-case delay multiplier.

- Macro intrinsic delays and extrinsic delays <u>are</u> multiplied by the worst-case delay multipliers.

- The worst-case multipliers used for the extrinsic net delays should be consistent with the macro type of the macro driving the net, i.e., nets driven by the input macros should use the interface macro worst-case delay multiplier.

- The worst-case delay multiplier for the extrinsic delay caused by output load capacitance is the <u>interface macro</u> worst-case delay multiplier.

- Delay multipliers at a given operating condition represent 20% on-chip signal tracking.

(803)

#### SELECTING THE CORRECT WORST-CASE DELAY MULTIPLIER

Commercial worst-case timing multipliers are for circuits operating in the 0°C ambient to 70°C ambient temperature range with a ±5% power supply variation and a junction temperature maintained at <130°C. Violation of any of these three parameters requires the use of the Military timing multipliers.

Military worst-case timing multipliers are for circuits operating in the  $-55^{\circ}$ C ambient to  $+125^{\circ}$ C case temperature range with a  $\pm 10$ % power supply variation and a junction temperature maintained at  $\leq 150^{\circ}$ C. If any of these parameters are violated, the military timing multipliers will no longer apply. Consult AMCC.

#### MINIMUM PROPAGATION DELAY

AMCC does not specify minimum circuit delays. However, a guideline for minimum propagation delay is 70% of the typical path delay (the annotated worst-case minimum multiplier is 0.70). Note that both the interface and the internal macros use the same worst-case minimum multiplier.

Where the performance of a circuit would be affected by excessive speed in an array, the minimum performance requirements must be clearly documented in the design submission.

#### RESULT

The interface macros, both input and output, use a <u>different</u> worst-case delay multiplier than the internal macros. The nets driven by interface macros use the interface macro worst-case delay multiplier. The nets driven by the internal macros use the internal macro worst-case delay multiplier.

To find path propagation delay, first add the intrinsic and extrinsic delays of the input and output macros for the path and multiply the sum by the correct interface worst-case delay multiplier. The extrinsic delay for an output macro is the delay caused by the system capacitive load and the package pin capacitance.

Second, total the intrinsic and extrinsic delays for all internal macros in the path and <u>multiply the sum by the proper internal worst-case delay multiplication factor</u>. Sum this result with the one found for the interface macros to find the total path propagation delay.

#### ASYMMETRY IN THE WORST-CASE PATH

Each potentially critical path must be evaluated for worst-case conditions. Both the propagation delay of a rising edge input signal and that of a falling edge input signal must be computed and compared for pulse stretch and pulse shrink. For multiple-input macros, the worst-case specification may be with one or more inputs switching or not. The worst potential circuit behavior represented by the macro specifications must be reviewed.

Minimum pulse-width requirements must be verified and the minimum path delay adjusted as necessary to meet these requirements.

In some cases the <u>minimum</u> delay may be the worst case. AMCC MacroMatrix releases contain the NOMINAL, MAXIMUM-MILITARY, MAXIMUM-COMMERCIAL and MINIMUM timing libraries for the array series.

AMCC design submission requirements include the simulation of the circuit for both the maximum worst-case (MIL or COM) and the minimum worst-case for functional, at-speed and AC test simulations.

It is up to the designer to provide similation vectors that will exercise the correct worst-case conditions for the macros in the critical path, whether it is for one input on a macro switching and the others remaining constant or for multiple simultaneously-switching inputs on a macro.

If there is a difference in the functional or AC test simulation results between the maximum and the minimum worst-case timing, hazard and race conditions are indicated and must be evaluated.

#### INTERNAL SIGNAL TRACKING

Many factors affect the signal delay tracking within the array. These factors include such things as relative position within the device, process variations, power supply variations, operating temperature and the characteristics of the various macros.

In BiCMOS, for interface macros, a "like structure" is defined as a similar macro type with the same option and fan-out load limits. For internal macros on Basic cells, the macros must actually be identical to be considered a "like structure".

- For like structures, for the same edge (both rising or both falling), and with placement on adjacent rows or cells within a quadrant, the tracking will be ±2.5%.

- $\bullet$  For like structures, for the same edge (both rising or both falling), and with a random placement, the tracking will be  $\pm 5$ %.

- For unlike structures, for the same edge (both rising and falling), and with a random placement, the tracking will be  $\pm 10$ %. (See Table 3-4.)

#### EXAMPLE OF TRACKING FOR THREE OPERATING CONDITIONS:

| - a +<br> /// // | - b +                              | - c +            |

|------------------|------------------------------------|------------------|

| 0.7<br>MINIMUM   | 1.0<br>NOMINAL<br>INTERFACE MACROS | 1.45<br>MILITARY |

| - a +            | - b +<br> /// //                   | - c +            |

| 0.7<br>MINIMUM   | 1.0<br>NOMINAL<br>INTERNAL MACROS  | 1.95<br>MILITARY |

From the diagram, for unlike structures, 1.1 \* c = 1.45 for an interface macro, 1.1 \* c = 1.95 for an internal macro.

#### SIGNAL BALANCING; DISTORTION MINIMIZATION

The case where two paths are required to be identical in performance is common. The best results are obtained when the macros are identical macros and are identically loaded, including wire load. Since placement cannot be assumed to be able to solve all problems in all cases, the judicious use of parallel structures (such as buffer trees) to reduce loading in a path and the use of pulse distortion minimization techniques, such as inversion of the signal at each macro, will help.

For ECL output operation at 100MHz and above, pulse distortion minimization methods should be used. These include: 1) signal inversion on alternating macros; 2) short interconnect, a function of fan-out and metal length; and 3) balanced rising-edge and falling-edge k-factors.

The final analysis for pulse stretch and shrink and balanced path delays must be performed using Back-Annotation.

#### MAXIMUM OPERATING FREQUENCY

The Q14000 Series is capable of supporting high I/O switching rates. The following is a summary of I/O and internal logic performance capabilities:

TABLE 3-6

MAXIMUM OPERATING FREQUENCY

PULSE WIDTH GUIDELINES

Q14000 SERIES B1CMOS ARRAYS

| TYPE OF I/O:                     | COM  | COM   | MIL | MIL   |

|----------------------------------|------|-------|-----|-------|

|                                  | MH z | PW-ns | MHz | PW-ns |

| TTL INPUT - S-OPTION - H-OPTION  | 65   | 7.69  | 60  | 8.33  |

|                                  | 90   | 5.55  | 85  | 5.88  |

| TTL OUTPUT - S-OPTION - H-OPTION | 50   | 10.00 | 45  | 11.11 |

|                                  | 65   | 7.69  | 60  | 8.33  |

| ECL INPUT - S-OPTION - H-OPTION  | 110  | 4.54  | 100 | 5.00  |

|                                  | 180  | 2.77  | 165 | 3.02  |

| ECL OUTPUT - S-OPTION - H-OPTION | 110  | 4.54  | 100 | 5.00  |

|                                  | 180  | 2.77  | 165 | 3.02  |

| INTERNAL MACRO - F/F FAST        | 180* | 2.40  | 165 | 3.02  |

| - F/F SLOW                       | 174  | 2.86  | 138 | 3.62  |

| - OTHER **                       | 165  | 3.02  | 130 | 3.84  |

<sup>\*</sup> limited by maximum driver frequency

Flip/flop, latch, counter and shift register documentation includes typical pulse width specifications. Pulse width is computed based on a 50% duty cycle. Selected MSI macros (those with flip/flops or latches with feedback paths) also carry specifications for maximum operating frequency.

To achieve the maximum toggle frequency for the fast flip/flops, they must be directly driven by ECL interface macros. There is no timing error generated by the timing analysis programs on the EWS simulators when a macro is driven faster than it is specified to run.

<sup>\*\*</sup>Gate macros GT01, GT02, GT03, GT11, GT12, GT33, GT44, and GT47 have a maximum frequency of 65MHz MILITARY and 82MHz COMMERCIAL. Their pulse width requirements are 3.93ns TYPICAL, 6.09ns COMMERCIAL and 7.66ns MILITARY. For faster versions of these macros please consult AMCC.

#### FRONT-ANNOTATION LOAD UNITS

The Front-Annotation statistical wire load unit table was calculated using the following:

| TABLE 3-7 |     |          |          |     |  |  |

|-----------|-----|----------|----------|-----|--|--|

| FRONT-    | -Al | NOTATION | LOAD UNI | T\$ |  |  |

|           |     | Q2100B   | Q9100B   |     |  |  |

|           |     |          |          |     |  |  |

| a         | 1   | 1.00     | 1.18     | - 1 |  |  |

| b         | 1   | 0.66     | 0.90     | ı   |  |  |

|           |     |          |          |     |  |  |

#### BACK-ANNOTATION LOAD UNITS

The Back-Annotation delay file is derived using the following:

TABLE 3-8

BACK-ANNOTATION DELAY MULTIPLIERS

| first layer metal  |      | LU/mm |

|--------------------|------|-------|

| second layer metal | 3.00 | LU/mm |

|                    |      |       |

# Section 4: External Tsu, Th

| EXTERNAL SET-UP AND HOLD TIM |

|------------------------------|

|------------------------------|

| -  | _ |    |     |   |

|----|---|----|-----|---|

|    | a | Λ  | -   | 3 |

| ٠. | o | LJ | . 1 | п |

| Table of Contents                                                                                        | 4-2 |

|----------------------------------------------------------------------------------------------------------|-----|

| External Set-Up and Hold Times                                                                           | 4-3 |