BUS INTERFACE

DISC BIT INTERFACE DRIVE

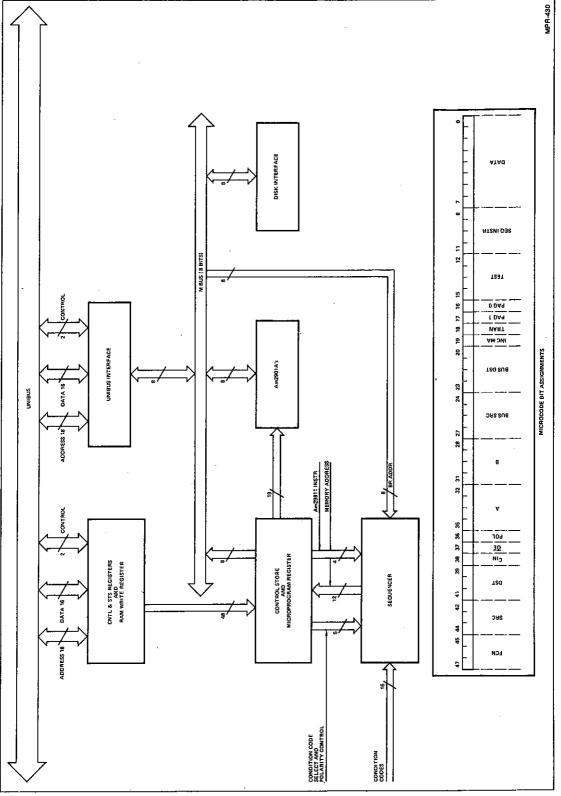

**SLICES**

Advanced Micro

CONTROL

STORE

SEQUENCER

# A HIGH PERFORMANCE DISC CONTROLLER

#### INTRODUCTION

The Am2901A Four-Bit Bipolar Microprocessor Slice, a significant advance in the state-of-the-art technology in Low-Power Schottky Integrated Circuits, enables the Design Engineer to implement new systems with higher logic density, better cost-effectiveness, and improved product versatility. The higher logic density and better cost-effectiveness of microprocessor-based designs is well-known and will not be discussed here. This application note, describing a Pertec D3441 Disc Controller for the Digital Equipment Corporation (DEC) PDP-11, will demonstrate how improved product versatility can be achieved by employing the Am2901A in the design of a peripheral controller.

This disc controller design is not intended to be an example of a minimal logic, cost-effective controller only one step away from the marketplace. Instead, think of it as the grandfather. Its large, writeable microprogram control store and its generalized disc and UNIBUS interface make it suitable to be the prototype for a family of disc controllers. Individual controllers would use ROM's of the appropriate size for the control store, and the disc interface would be tailored to a particular disc drive.

#### THE DISC CONTROLLER

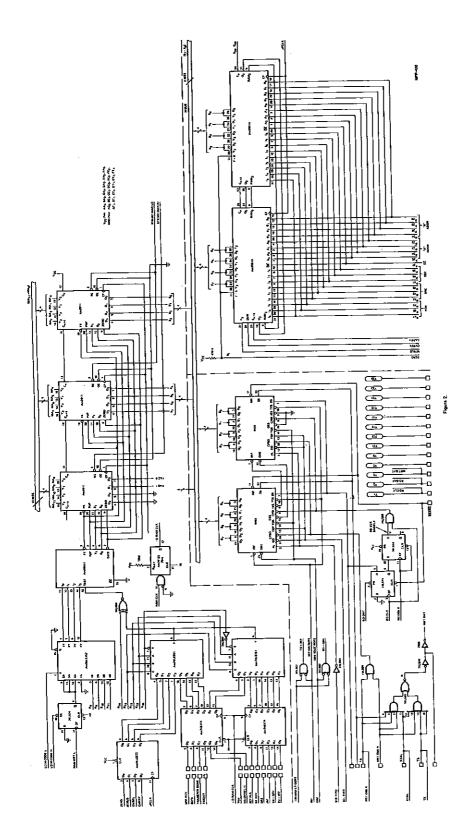

A major advantage of designing with microprocessors is that the designs tend to be highly structured and therefore much easier to comprehend. Referring to Figure 1, notice that the disc controller is composed of a small number of well-defined sub-sections. Each sub-section will be discussed in detail and then the interaction between sub-sections will be described. The reader will find that the individual sub-sections are easy to understand because each one has a limited but well-defined role in the disc controller.

#### THE MICROPROCESSOR

The microprocessor, 8 bits wide using two Am2901A's, provides the disc controller with an arithmetic and logic capability. In this application, the arithmetic capabilities of the Am2901A are not taxed. Mainly, they are used to generate checksums on disc reads. The principal role of the microprocessor in this design is that of a logic processor. As the reader will discover further on, both the DEC UN-IBUS interface and the disc interface are very general purpose. It is the logic processing power of the Am2901A, coupled with the control information of the microprogram, that enables the disc controller to completely emulate the RK11 disc controller (SSI TTL controller from DEC). If the disc controller is considered as a state machine, at any given instance, the current state of the machine is to a large degree defined by the contents of the microprogram register. When an unexpected state is encountered, the logic processing power of the microprocessor enables it to exercise more control over the selection of the next state to enter. In the disc controller, this is evidenced more through error recovery procedures.

All recoverable errors can be handled by the disc controller without the intervention of the host computer. In addition to supplying logic processing power, the microprocessor also provides seventeen high-speed, 8-bit temporary storage registers. Most of these registers are assigned specific functions. In this application, twelve registers were used to build six 16-bit registers. These registers contain the disc address, memory address, transfer word count, control and status information, error information, and the checksum. Of the remaining five registers, four are utility registers that are employed as needed, and the fifth is the Q register which can be used to store and retrieve 8-bit values.

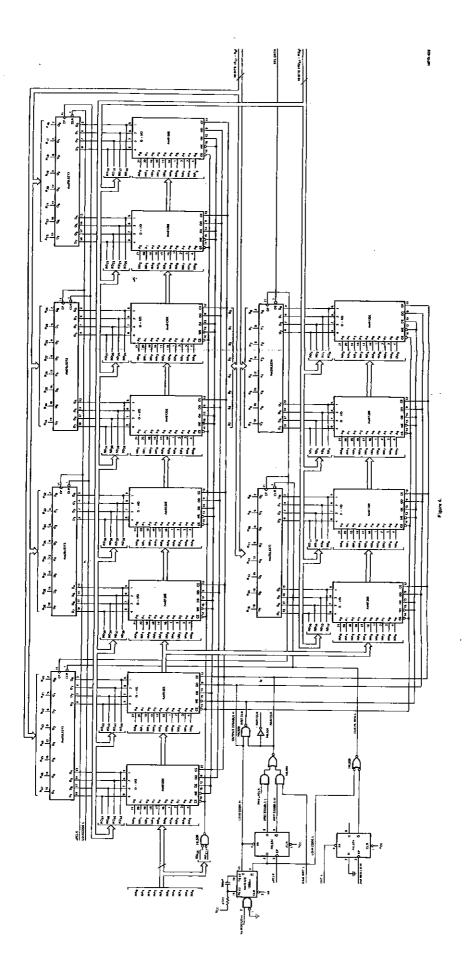

Figure 2, depicting the two Am2901A's, shows that the microprocessor interface to the other sub-sections is very simple. The 8-bit bidirectional M bus (microprocessor bus) enables the microprocessor to input/output data from/to the other subsections of the disc controller. Four condition lines (ZERO, MINUS, OVRFL, and CARRY) communicate the resulfs of logic and arithmetic operations to the sequencer, which may select one of these lines to determine the address of the next microinstruction. Notice that since the condition lines are latched, the sequencer is always looking at the conditions of the previous microinstruction. On each clock cycle, the Am2901A's are presented with a 19-bit instruction from the microprogram register. This 19-bit instruction consists of a 9-bit microinstruction decode, an 8-bit register select, the carry-in, and the output enable (see Figure  $\bar{3}$ ). By the end of the clock cycle, the specified arithmetic or logic operation has been performed, the result has been stored, and the condition codes have been latched. The microprocessor is now ready to perform the next instruction.

#### THE SEQUENCER

A microinstruction usually has two primary parts. These are: (1) the definition and control of all elemental microoperations to be performed, and (2) the definition of the address of the next microinstruction to be executed. Referring back to the consideration of the disc controller as a state machine, it is evident that the controller's ability to perform any useful function is dependent on its ability to progress from state to state in a controller manner. It is the task of the sequencer to provide control over the transitions from state to state.

In order to provide this control, some feedback from various system components is necessary. For example, when reading a word from PDP-11 main memory, the controller must first request the UNIBUS by asserting NPR (non-processor request). The controller then enters a waiting state and the sequencer will keep the controller in this state until the signal NPR RDY informs the sequencer that the UNIBUS is now available for the transfer. At this time, the sequencer will transition the controller into the next state which would start driving the address onto the UNIBUS and assert MSYN (master sync). The sequencer designed for this controller (see Figure 2) provides for up to sixteen different input condi-

Figure 1.

| 18 | 17                      | 16 | 15              | 14 | 13 | 12            | 11 | 10                    | 9 | 8 | 7                     | 6 | 5 | 4        | 3                 | 2 | 1 | 0 |

|----|-------------------------|----|-----------------|----|----|---------------|----|-----------------------|---|---|-----------------------|---|---|----------|-------------------|---|---|---|

|    | TINAT                   |    | ALU<br>FUNCTION |    |    | ALU<br>SOURCE |    | A REGISTER<br>ADDRESS |   |   | B REGISTER<br>ADDRESS |   |   | C A I    | 1 U O             |   |   |   |

|    | MICROINSTRUCTION DECODE |    |                 |    |    |               |    | REGISTER SELECT       |   |   |                       |   |   | R N<br>Y | P B<br>U L<br>T E |   |   |   |

Figure 3.

tions. On each microcycle, four bits from the microprogram register will select one of the sixteen input conditions. The selected condition is XOR'ed with another bit from the microprogram register to provide polarity control over the selected conditions as it is inputted to the Am29811.

The Am29811, the next address control unit, can execute sixteen different next address control functions, most of which are conditional. Thus, the device requires four instruction inputs as well as the condition code test input. The four instruction inputs come from a multiplexer that normally selects the Am29811 instruction specified in the microprogram register. However, when the writeable control store is being loaded, the multiplexer selects the other input, which forces the Am29811 to execute JUMP ZERO on the first write cycle and CONTINUE on all following write cycles.

The outputs of the Am29811 are used to control the stack pointer and the next address multiplexer of the three Am2911's. These three Am2911's are cascaded to form the 12-bit microprogram sequencer. The Am2911's can select an address from any of three sources. They are: (1) external data from the D inputs, stored in an internal register; (2) a four-word deep push/pop stack; or (3) a program counter register (which usually contains the last address plus one). The push/pop stack includes certain control lines so that it can efficiently execute nested subroutine linkages. The internal register that is loaded from the M bus appears to the rest of the system as just another M bus destination. At the end of a bus cycle, if the two low-order Am2911's or the high-order Am2911 has been selected as the M bus destination, the selected Am2911's register enable will be strobed to clock in the data on the M bus. Once the internal register is loaded, it can be selected on any following microinstruction as the source of the next address.

#### THE CONTROL STORE

The output of the microprogram sequencer is a 12-bit address that selects the next microinstruction to be fetched from the control store. At the beginning of each microcycle, the output of the control store is strobed into the microprogram register. Since this register holds the microinstruction while it is being executed, the memory is free to fetch the next microinstruction as soon as the sequencer can determine the address of the next instruction. This technique, referred to as pipelining, allows the fetching of the next microinstruction to be overlapped with the execution of the current microinstruction.

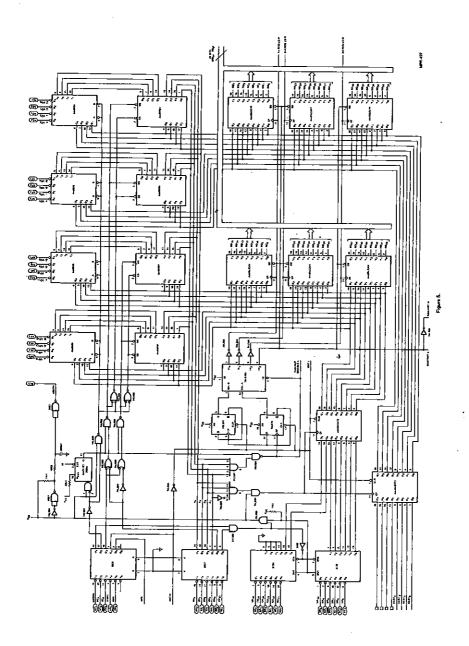

The disc controller's control store, 48 bits wide by 1K deep, is comprised of twelve Am9130's (see Figure 4). The Am9130 is a high-performance, low-power, 4096-bit, static, read/write memory organized as 1024 words by 4 bits per word. The data input and output signals are bussed together and share common I/O pins.

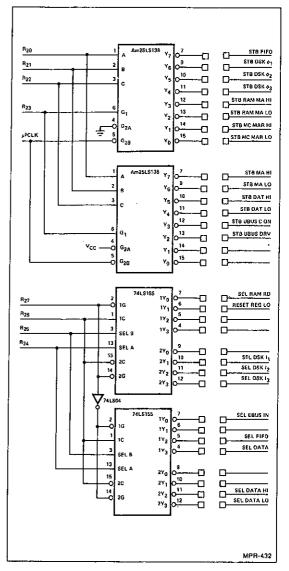

The microprogram register is comprised of six 8-bit registers. The low-order register holds the data portion of each microinstruction. This register, an Am25LS374, has three-state outputs and when selected as a bus source, it will drive the data onto the M bus. The other five registers are Am25LS273's, which consist of D-type flip-flops with a common clock and a common clear.

Normally, the control store is clocked by the microprocessor clock ( $\mu$ PCLK). However, when the control store is being loaded by the PDP-11, it is clocked every time a 48-bit word, assembled in the RAM Write Register, is ready to be written into the control store. When a millisecond has passed without a RAM write cycle, a one-shot times out (the signal LD MCODE is no longer asserted), and the control store is once again clocked by  $\mu$ PCLK. While LD MCODE was asserted, the clear input to the microprogram register was also asserted and the output of the Am9130's was disabled.

#### THE CONTROL AND STATUS REGISTERS

To provide for communication between the PDP-11 CPU and the disc controller, sixteen 16-bit registers have been interfaced to the UNIBUS (see Figure 5). Except for the fact that the last two registers play a special role in loading the control store (determining the address of these registers on the UNIBUS) and in selecting the frequency of the  $\mu PCLK$ , these registers are just memory locations. Indeed, core memory locations could be used for the control and status registers. The only disadvantage to doing this would be that the controller would not be compatible with existing software.

The disc controller uses the same procedure for reading or writing the control and status registers as it does when reading or writing in main memory. This approach has the advantage of using the UNIBUS arbitration logic to solve the problem of both the CPU and the controller accessing the same control and status register at the same time.

Since the control and status registers are just memory locations, the definition of what each group of bits means is totally determined by the microprogram. As the same controller is used to interface different types of disc drives, the microcode can define the control and status registers to be compatible with whatever PDP-11 disc system is to be emulated.

As was mentioned earlier, the last two registers are special. When data is written into the last register, it is also stored in one of the RAM WRITE REGISTERS. Which register is selected is determined by a 2-bit counter that is incremented after each write. Every fourth write is a signal that 48 bits have been accumulated in the RAM WRITE REGISTER and it is time for the control store to perform a write cycle. Example 1 is a listing of PDP-11 code that would load the control store from a 3K word buffer in main memory.

;LOADCS is entered with R0 a pointer to the buffer ;and R1 a pointer to the last device register (160016).

LOADCS:

RESET

:initialize 2-bit counter and :cause LDMCODE to be asserted

LOOP: MOV (R0)+, (R1)

MOV (R0)+, (R1)

:load 48-bit RAM

MOV (R0)+, (R1)

:WRITE REGISTER

CLR (R1)

CMP RO, #BUFEND

phony write to cause control store write ;condition : has all of the buffer been copied?

**BLO LOOP** RTS PC

;if no, then branch

;if yes, then return

Example 1. PDP-11 Code to Load Control Store.

Whenever the second to last register is written, the data is also stored in a 16-bit internal register. The high-order byte is used to set the UNIBUS address of the control and status registers. Initially, the base device register address was 160000g, because the INIT pulse on the UNIBUS (caused by power-up or the RESET instruction) cleared the 16-bit internal register. It is up to the PDP-11 to keep track of the current address of the control and status registers as they are moved about. Also, the PDP-11 must somehow let the controller know where its registers are. Usually, this information is contained in the microcode. This ability to change the address of the device registers allows the controller to attempt to emulate just about whatever it wants to emulate.

The low-order four bits of this internal register can be set by the PDP-11 to select 1-of-16 microprocessor clock rates. It is not clear that this is very useful, but in a general purpose prototyping design, why not?

#### THE UNIBUS INTERFACE

The UNIBUS interface consists of two main parts: (1) the transceivers for the address, data, and control lines; and (2) the handshaking logic required to control UNIBUS trans-

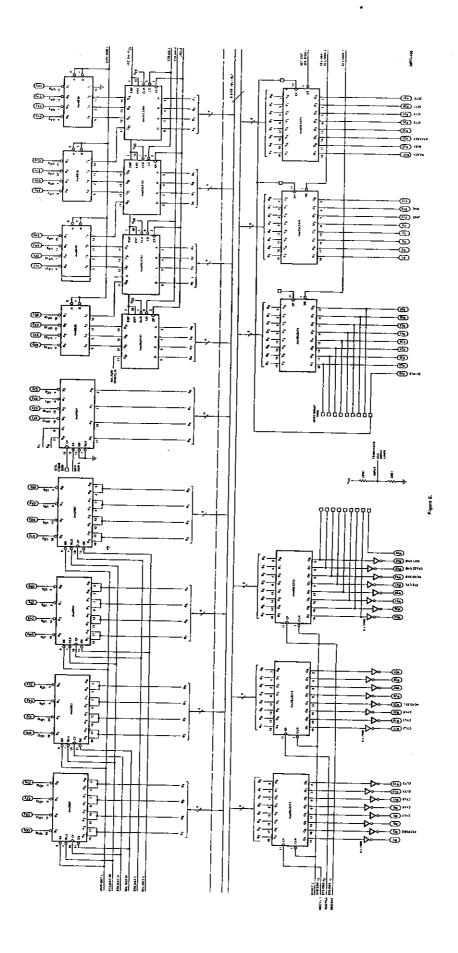

Figure 6, depicting the address, data, and control line transceivers, illustrates that the microprocessor communicates with the transceivers via registers which can act as either sources or destinations for the M bus. The registers for the address line transceivers (in this case used only as line drivers) are synchronous 4-bit counters (Am25LS161). In a DMA transfer, the starting address would be initially loaded into the Am25LS161's in two M bus cycles. On the first cycle, the low-order byte of the address register would be loaded. The second cycle would load the high byte. Once the memory address register has been initialized to the transfer starting address, it can be incremented to successive memory locations at the end of each transfer by the assertion of INC MA. The output of the address register is shifted one bit position as it is fed into the UNIBUS drivers to compensate for the fact that each byte has a unique address in the PDP-11, and the controller only addresses word locations.

Am2907's are used as the transceivers for the UNIBUS data lines. Internal to the Am2907's are the data input and the data output registers. On a UNIBUS read cycle, data is strobed into the data input register from the UNIBUS when SSYN (Slave Sync) is received. The data is then available to the

microprocessor via the M bus. On a UNIBUS write cycle, data is first loaded into the data output register via the M bus, and then the UNIBUS write transaction is initiated.

Another Am2907 is used for the control lines and the two high-order address lines. These control and address lines are initialized before the start of a DMA transfer. The control lines never need to be changed during a DMA burst. However, if the memory address register should overflow, the two high-order address bits will need to be updated before the next UNIBUS read or write transaction.

In addition to the address, data, and control lines, the UN-IBUS has additional signals which provide synchronization for data transfers, allow control of the UNIBUS to be passed to any DMA controller, and provide an interrupt capability.

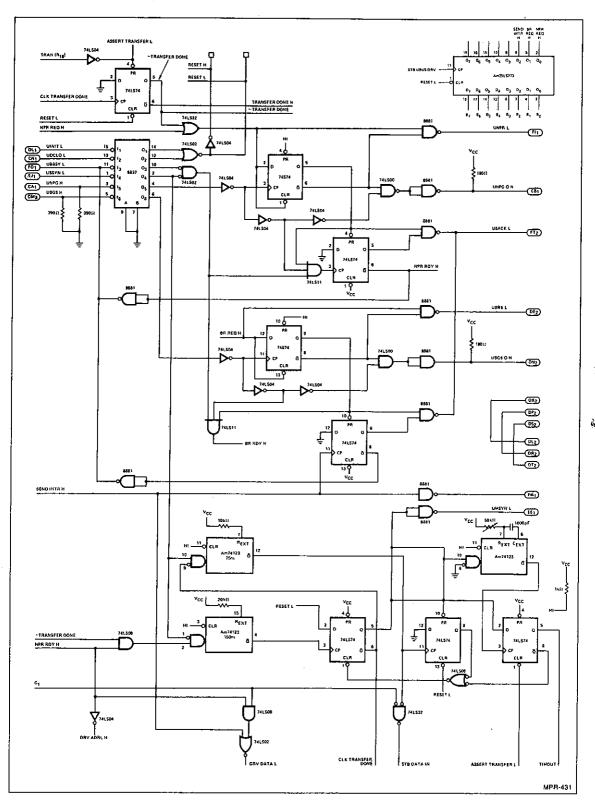

Figure 7 is the diagram of the UNIBUS handshaking logic. The microprocessor may request the UNIBUS by asserting NPR REQ or BR REQ, depending on whether the bus is being requested for a DMA transfer or an interrupt transaction. When the handshaking logic has gained control of the UN-IBUS, the microprocessor will be informed by the assertion of either NPR RDY or BR RDY. For a read or write transaction, TRAN is asserted to initiate the data transfer. Coming to the microprocessor's aid once again, the handshaking logic will sequence through UNIBUS protocols and inform the microprocessor of the completion of the transfer by asserting TRANSFER DONE.

#### THE DISC INTERFACE

The disc interface is comprised of a 24-bit parallel input port and a 24-bit parallel output port (Figure 6), and an 8-bit wide, 16-word deep FIFO (Figure 2). The input and output ports are "soft", in that the function of the individual bits are defined in the microcode. Since both ports are quite wide, almost any disc based on 2314 technology can be accommodated by the controller.

The input port receives status information and control signals from the disc drive. Status information generally includes the sector counter, the index and sector pulses, error conditions, and unit attention. Any control signals from the drive that are used to strobe data into registers should be received on a line with a wire-wrap pin. This allows for simple gating of the control signals to generate data strobes.

The output port transmits control information, such as cylinder address, head select, read and write enable, and unit select, to the disc drives.

Figure 7.

The FIFO performs parallel-to-serial conversion on data that is being written on the disc and serial-to-parallel conversion on data that is read from the disc. When writing, the FIFO is clocked by a crystal oscillator at whatever frequency is required by the disc drive. However, when reading data from the disc, the FIFO is clocked by the RD CLK signal from the disc drive.

In addition to converting from parallel-to-serial and vice versa, the FIFO provides buffering between the controller and the disc drive. For example, before a disc write is initiated, the 16-word deep FIFO will have been filled. Each time a byte is dispatched to the disc, the contents of the FIFO will schuffle down and the microprocessor will be signalled that there is room for another byte in the FIFO. If the controller experiences a delay in gaining control of the UNIBUS to fetch the next word, the 16-byte buffer within the FIFO will enable it to keep sending serial data to the disc in sync with the write clock. Once the controller gains control of the UNIBUS, it should not release it until enough data has been read from main memory to refill the FIFO.

#### THE M BUS

The microprocessor bus is the main communication path that links the various subsections of the disc controller together. On each microcycle, the M bus can perform one 8-bit data transfer between a bus source and a bus destination. At the beginning of the microcycle, the selected bus source begins driving data onto the M bus. After a short propagation delay, the data is available to all destinations on the M bus. At the very end of the microcycle, the data on the M bus will be strobed into the selected destinations.

The M bus sources and destinations are selected by 4-bit fields in each microinstruction (refer to Figure 8). Therefore, the M bus can have up to 15 sources and 15 destinations. In addition, the microprocessor can be either a source or a destination. Notice that if the microprocessor is not using the M bus during a microcycle, the M bus is free to perform a data transfer in parallel with whatever the microprocessor is doing. Also, it is sometimes useful for the microprocessor to be a second M bus destination. For example, when the controller is reading data from the disc, as each byte is transferred from the FIFO to either the high- or low-order UNIBUS data register, the microprocessor also receives the data on the M bus and adds it to the partially formed checksum. Thus, the microprocessor is kept busy building the checksum, while the M bus is being used as the data path between the disc interface and the UNIBUS interface. This parallel operation ability of the controller becomes important when the data rate of the disc drive approaches the transfer capacity of the controller because the controller's capacity is directly related to the number of microinstructions that must be executed on each pass through the inner loop of the disc write or disc read code.

### THE CLOCK

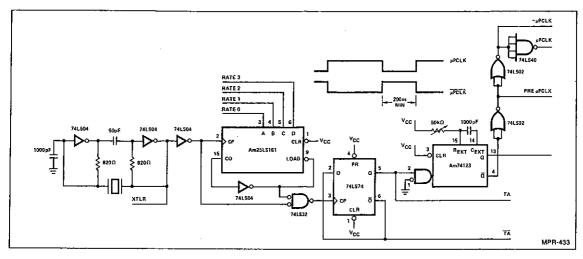

Figure 9 is a logic diagram of the disc controller clock which is the main source of synchronization signals within the controller. The Am25LS161 provides the ability to select multiples of the basic crystal frequency as the output of the clock circuit (see Table I). The duty cycle of the clock can be varied by adjusting the trimpot on the Am74123 One-Shot.

The crystal is selected to provide the proper frequency for the disc drive to be interfaced. Disc drives based on 2314 technology use the double frequency recording method,

Figure 8.

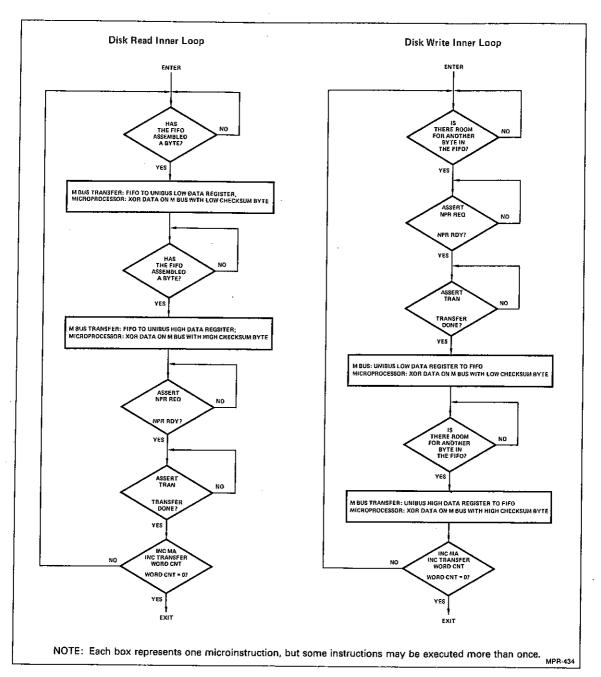

which means that every other pulse is a clock pulse and the presence or absence of pulses between the clock pulses defines "ones" and "zeros". The crystal frequency must be the same as the double frequency when writing all "ones". If RATE is set to 17, then the frequency of µPCLK will be one-half the crystal frequency (see Table I), and the microprocessor will cycle once for every data bit received from the disc. This implies that for a 16-bit computer, 16 is the maximum number of microinstructions that can be executed on each pass through the inner loop of the disc read or disc write microcode. (Refer to Appendix I to find examples of the inner loop for reading and writing.) Any more and the controller will gradually fall behind until either the FIFO overflows (disc read) or runs out of data (disc write). It might be possible to clock the microprocessor as fast as it will run, and clock only the FIFO in sync with the disc drive (thus allowing

Figure 9.

| Rate Input μPCLK Frequency  17 XTLR/2 16 XTLR/4 15 XTLR/6 14 XTLR/8 13 XTLR/10 12 XTLR/10 12 XTLR/12 11 XTLR/16 7 XTLR/16 7 XTLR/18 6 XTLR/20 5 XTLR/20 5 XTLR/22 4 XTLR/24 3 XTLR/24 3 XTLR/26 2 XTLR/28 1 XTLR/30 0 XTLR/32 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

Table I. Selecting µPCLK Frequency.

more microinstructions per word transferred), but strange problems with roots based in the beat frequency between the microprocessor clock and the FIFO clock would be likely to occur.

#### INTERACTION OF CONTROLLER SUB-SECTIONS

Now that each sub-section has been described, it should be instructive to step through a disc transfer operation and observe the interaction of the controller sub-sections. Initially, the controller, in its idle state with no error conditions present, is looping on the SECTOR PULSE condition line. When SECTOR PULSE, a signal from the disc drive, goes "true", the controller loads the address of its control and status register into the UNIBUS address register, sets the control lines for a read operation, and then requests the UNIBUS by asserting NPR REQ. When control has been

granted (signalled by the assertion of NPR RDY), the controller asserts TRAN to start the UNIBUS read cycle. The assertion of TRANSFER DONE signals that the control and status register has been read and the data is in the UNIBUS data register.

If the low-order bit of the control and status register is not set, then no operation has been requested. The controller will fall back into its idle loop as soon as it updates the disc status register, which contains the sector number of the sector currently under the heads.

If the low-order bit was set, then the next low-order three bits define the function to be performed. However, before dispatching to the appropriate routine for whatever function is to be performed, the controller reads the memory address, word count, and disc address for the upcoming transfer from its device registers and copies the data into its internal registers (these are the registers within the Am2901A's). Assuming, for this example, that the function is a disc read, the controller dispatches to the read microcode.

The first microinstruction of the read routine is a subroutine call to the SEEK routine. This routine loads the cylinder address, derived from the disc address, into the output port of the disc interface. The following microinstruction asserts the CYLINDER ADDRESS STROBE on another line in the output port. CYLINDER ADDRESS STROBE is then removed and the controller loops until the drive indicates that the seek has been completed. The SEEK subroutine then selects the proper head (again derived from the disc address) and finally starts looping on SECTOR PULSE. Each time a sector pulse is detected, the controller checks if this is the sector specified in the disc address. If it is, SEEK returns control to the microinstruction following the one that made the call on SEEK. Notice that SEEK doesn't just seek to the desired cylinder, it seeks the sector specified in the disc address.

When control returns to the disc read microcode, the controller waits about  $100\mu s$  and then asserts READ ENABLE, one of the lines in the output port of the disc interface. At this time, the preamble should be under the enabled head. The preamble is a string of "zeros" terminated by a "one" bit. The "one" bit signals that the data record follows immediately. The first "one" bit will set a flip-flop and assert RD CLK ENABLE (see Figure 2), which will enable the RD CLK from the drive to

start clocking data into the FIFO. Control now falls into the "disc read inner loop" microcode (flowcharted in Appendix I). In this loop, each time a byte is assembled in the FIFO it is copied alternately to the low-order UNIBUS data register and then to the high-order data register. As the data is copied from the FIFO to the data register, the checksum is built by the microprocessor. Every time the high data register is loaded, it is time to transfer another word into PDP-11 main memory. At the end of each UNIBUS transfer, INC MA is asserted to advance the UNIBUS memory address register to the next word address. The transfer word count is then decremented and if not zero another iteration through the "inner loop" is required. When the transfer word count reaches zero, the entire sector has been transferred, and the next word read from the disc is the checksum. This is compared with the checksum that has been built by the microprocessor. If they are not equal, the controller may attempt a retry, or it may just set the checksum error bit in the disc error register and continue as if there were no error. Assuming there wasn't any checksum error, the controller now drops READ ENABLE and the read has been completed. The controller now has only to update its external device registers from the internal set and it is back where first started; in the idle state.

Notice that the external device registers were updated only at the successful completion of the transfer. Therefore, whenever any error condition is encountered, the controller always has the complete information necessary to perform as many retries as the microcode dictates.

#### SUMMARY

Greater product versatility can be achieved by employing the Am2901A in the design of peripheral controllers. Indeed, there is nothing in the design discussed in this app note that says it has to be a disc controller. The FIFO is the only hardware that "leans" in the direction of a disc controller, and it does so only by virtue of the way it is clocked. But don't forget that the FIFO is just a general purpose, buffered parallel-to-serial and serial-to-parallel converter.

To stress this point of product versatility, let us briefly consider what would be necessary to convert this DEC RK11/RK05 compatible disc controller into a DEC TM11/TU10 mag tape controller. First, remove the FIFO. Next, re-label Figure 6 to read "Mag Tape Interface". Then connect a cable from the mag tape interface to whatever mag tape drive has been selected. Finally, write the microcode that will enable this hardware to emulate the TM11/TM10.

Voila!

NOTE: Advanced Micro Devices wishes to acknowledge the contributions of William Pitts in the design and implementation of this application note.

#### **PARTS LIST**

| Device    | Description                             | Qty. | Device  | Description                       | Qty. |

|-----------|-----------------------------------------|------|---------|-----------------------------------|------|

| Am2901A   | Four-Bit Bipolar Microprocessor Slice   | 2    | 74574   | Dual D-Flip-Flop, Positive        |      |

| Am2907    | Quad Bus Transceiver with               |      |         | Edge-Triggered                    | 1    |

|           | Three-State Receiver and Parity         | 5    | 74LS00  | Quad 2-Input NAND Gate            | 3    |

| Am2911    | Microprogram Sequencer                  | 3    | 74LS02  | Quad 2-Input NOR Gate             | 2    |

| Am29701   | Non-Inverting 64-Bit RAM                |      | 74LS04  | Hex Inverter                      | 5    |

|           | with Three-State Outputs                | 4    | 74LS08  | Quad 2-Input AND Gate             | 4    |

| Am29811   | Next Address Control Unit               | 1    | 74LS11  | Triple 3-Input AND Gate           | 1    |

| Am25LS138 | One-of-Eight Decoder/Demultiplexer      | 2    | 74LS21  | Dual 4-Input AND Gate             | 1    |

|           | Quad 2-Input Multiplexer with           |      | 74LS32  | Quad 2-Input OR Gate              | 1    |

|           | with Non-inverting Outputs              | 1    | 74LS40  | Dual 4-Input NAND Buffer          | 1    |

| Am25LS161 | Synchronous 4-Bit Binary Counter        |      | 74LS55  | 2-Wide 4-Input AND-OR-Invert Gate | 2    |

|           | with Asynchronous Clear                 | 5    | 74LS74  | Dual D-Flip-Flop, Positive        |      |

| Am25LS273 | 8-Bit Register with Common Clear        | 12   |         | Edge-Triggered                    | 7    |

| Am25LS374 | 8-Bit Register with Three-State Outputs | 10   | 74LS86  | Quad 2-Input Exclusive OR Gate    | 1    |

| Am74123   | Dual One-Shot Multivibrator             | 4    | 74LS155 | Dual 2-to-4 Decoder/Demultiplexer | 3    |

| Am74LS251 | 8-Input Multiplexer with                |      | 8136    | 6-Bit Unified Bus Comparator,     |      |

|           | Three-State Outputs                     | 2    |         | Open Collector                    | 2    |

| Am74S174  | Schottky 6-Bit High Speed Register      | 2    | 8837    | Single Ended Line Receiver        | 3    |

| Am8838    | Quad Unified Bus Transceiver            | 8    | 8881    | Quad 2-Input NAND Gate            | 3    |

| Am9130E   | 1024 x 4 N-Channel Static RAM           | 12   | 9403    | First-In-First-Out (FIFO)         |      |

| 7406      | Hex Inverter                            | 5    |         | Buffer Memory                     | 2    |

| 7400      | LIGY IIIAQITGI                          | 3    |         | TOTAL                             | 120  |

NOTE: The crystal used in this particular design oscillated at 3.125MHz, and was chosen so that this disc controller would be compatible with the DEC RK11/RK05. Those desiring a different data transmission rate may choose a different crystal to suit their application.

<sup>&</sup>lt;sup>1</sup>Microprogramming Handbook; Mick, John R. and Jim Brick, Advanced Micro Devices, 1976.

<sup>&</sup>lt;sup>2</sup>PDP-11 Peripherals Handbook, Digital Equipment Corporation, 1975.

## APPENDIX II MICROCODE FOR RK11 SOFTWARE COMPATIBLE DISK CONTROLLER

```

WILLIAM M. PITTS

26 APR 77

I CONTROL RESET -- RESETS THE DISK CONTROLLER. THIS ROUTINE IS ENTERED

WHENEVER FINITY IS ASSERTED ON THE UNIBUS OR WHEN

THE FUNCTION *CONTROL RESET* HAS BEEN SPECIFIED BY

ŧ

J

THE PUP-11.

969

89 AØ 6Ø ØØ ØC ØØ

IRESET ALL INTERNAL REGS

001

89 AØ 70 ØØ @C ØØ

962

89 A8 88 88 8C 88

903

89 40 90 00 00 00

604

89 A0 A0 00 0C 00

905

89 AG BO OG OC OG

89 A0 C0 00 0C 00

886

907

89 AØ DF 60 ØC 62

ISET UNIBUS NA TO 177402

89 AO EF 70 OC FF

898

009

89 AB FF Ø1 81 Ø6

JCALL SUB FOR MEM WRITE

A DISK OPERATION HAS JUST BEEN COMPLETED, SO SET THE 'DONE' BIT &

CLEAR THE 'GO' BIT IN THE INTERNAL RKCS.

80A

75 A8 AF 00 UC 89

ISET 'DONE' BIT IN INTERNAL REG

998

95 A8 8F 00 0C FE

JCLR 'GO' BIT IN INTERNAL REG

NOW IT'S TIME TO UPDATE THE EXTERNAL REGISTERS.

00C

10 AØ 3F ØØ ØC 1Ø

IRESET ERROR RETRY COUNTER

880

11 AA 6F 60 0C 06

ISET UNIBUS MA TO 177406

11 AB 7F 70 0C FF

OBE

ICALL SUB TO UPDATE EXT REWC

00F

00 AG OF 01 81 95

818

11 AC 60 00 0C 00

011

11 AD 7F 01 81 07

JUPDATE EXTERNAL RKBA

11 AE 60 00 0C 00

012

JUPDATE EXTERNAL RKDA

013

11 AF 7F 01 81 07

014

11 A8 6F 60 0C 0A

PRESET UNIBUS MA TO 177404

015

11 A9 7F 01 81 06

JUPDATE EXTERNAL RKCS

;

IF INTERRUPTS ARE ENABLED, PERFORM INTERRUPT SEQUENCE.

94 A8 OF 88 OC 48

016

INTERRUPTS ENABLED ?

80 A0 OF 00 03 1F

INQ, THEN GO TO 'IDLE'

017

018

00 A0 0F 40 0C 90

JINTERRUPT VECTOR TO UNIBÚS DATA REG

019

00 AG OF SH OC 00

BIA

88 A8 OF 28 9C 48

PREDUEST UNIBUS FOR INTERRUPT

00 B0 OF 00 03 18

JLOOP HERE TILL WE'VE GOT THE UNIBUS

818

esc

28 A0 0F 20 0C 50

LASSERT INTERRUPT

810

20 80 8F 80 53 10

ILOOP TILL SSYN IS RECEIVED

00 A0 OF RO 0C 20

21E

IRELEASE UNIBUS

THE CONTROLLER WAITS FOR SOMETHING TO DO HERE IN THE 'IDLE' LOOP.

EVERY TIME A SECTOR PULSE IS SEEN, THE CONTROLLER READS THE EXTERNAL

RHCS TO SEE IF A DISK OPERATION HAS BEEN REQUESTED. ALSO, THE EXTERNAL

RKDS IS UPDATED AT THIS TIME.

01F

00 AO OF 60 OC 04

ISET UNIBUS MA TO 177404

00 AN OF 70 NC FF

020

00 B0 0F 00 A3 1F

021

ILOOP & WAIT FOR SECTOR PULSE

455

100 A0 OF 01 81 00

IREAD EXTERNAL RKCS

023

95 A6 8F 08 9C 7F

IMASK & COPY TO INTERNAL REG

024

95 A7 9F 08 0C 0F

00 A0 0F 01 81 01

925

TREAD EXTERNAL REDA

986

11 A6 E0 00 0C 00

JCOPY TO INTERNAL RKDA

11 A7 FF 60 UC 00

827

00 A0 OF 00 81 82

821

ISELECT SPECIFIED DISK DRIVE

I UPDATE EXTERNAL RKDS

229

1D A0 61 00 0C 00

JLOAD SECTOR COUNTER

```

; SET "ACCESS READY"

; CLR ALL BUT DRIVE SELECT

DS A6 6F 00 0C 40

ASB

826

```

950

05 A7 7F 88 8C 88

ISET 'RKOS'

080

88 AB OF 81 81 96

JUPDATE EXTERNAL REDS

85E

94 A8 OF 00 0C 01

1"GO" BIT SET IN RKCS ?

825

86 A8 6F 88 83 1F

INO, THEN LOOP & WAIT

A DISK OPERATION HAS BEEN REQUESTED. IF REQUESTED FUNCTION IS CONTROL RESET, GO DO IT. ELSE CHECK IF ANY HARD ERRORS ARE PRESENT. IF NO HARD ERRORS, UPDATE ALL INTERNAL REGISTERS AND THEN DECODE

THE REQUESTED FUNCTION AND DISPATCH TO THE APPROPRIATE ROUTINE.

938

89 AØ 1F 01 81 00

ICLR TEMP ERR REG (NOGO) & READ EXT RKER

631

94 AB OF BO OC OE

CONTROL RESET ?

932

80 A0 0F 00 03 00

IYES, SO DISPATCH

95 A6 6F 00 0C FC

033

IANY HARD ERRORS ?

80 80 0F 01 03 22

95 A7 7F 00 0C FF

034

JYES, THEN ABORT

835

THARD ERRORS ?

036

00 80 0F 01 03 22

IYES, THEN GO TO NOGO

037

80 A0 8F 60 8C 82

SUPDATE EXT RKER

036

88 A0 8F 81 81 86

039 ·

11 A6 60 00 0C 00

SCOPY INTERNAL RKCS TO LO & HI

11 A9 7F 01 81 07

03A

SUPDATE EXT RKCS

038

90 AD OF 61 81 69

JREAD EXT RKWC

03C

11 46 AØ ØØ ØC ØØ

F ... & COPY TO INTERNAL REWC

11 A7 BF 81 81 81

83D

TREAD EXT REBA

03E

11 06 CO 60 OC OD

I ... & COPY TO INTERNAL RKBA & UNIBUS MA

83#

11 07 00 70 00 00

848

25 EA CA 80 NC 80

JUPDATE INT REBA TO TRANSFER END

941

25 F6 DF 00 33 43

. +2

842

20 A0 D0 00 0C 00

843

25 EA CØ ØØ ØC ØØ

JAGAIN, SINCE REWC IS A WORD CHT

25 FB DF 00 33 46

.+2

20 40 00 00 00 00

045

J DISPATCH

046

96 A8 OF DO HC DE

JFUNCTION IS LOW 3 BITS OF RA

047

15 AO OF OO UC 48

10 80 PF 00 02 00

048

JMP TO ". + RO"

949

00 A0 NF 00 02 50

JWRITE

84 A

84 B

00 A0 0F 00 02 BC

IREAD

00 A0 OF 00 U2 BC

JWRITE CHECK

04C

88 AF 0F 00 02 FC

ISEEK

940

60 A0 0F 00 02 6C

JREAD CHECK

00 A0 OF 00 02 FE

84E

JORIVE RESET

04F

40 40 0F 08 02 0A

JWRITE LOCK

! WRITE OPERATION

950

95 AB OF OU UC 30

IMASK OUT ALL BUT MEM EXT BITS

11 00 00 30 00 00

051

#8ET 417, 416, C1, 8 C0

052

1D A0 11 00 00 00

IREAD SECTOR COUNTER

853

95 Å1 1F 00 MC 2M

JORIVE WRITE LOCKED ?

054

00 BU 0F 01 03 19

IYES, SO SET ERR BIT & ABORT

055

00 AD OF 00 81 88

ISEEK TO SPECIFIED CYLINDER

056

88 AG GG 50 GC 99

JRESTORE FIFO REGISTERS

957

00 A0 OF FO OC 00

ILOAD FIFO WITH 2 FOF BYTES

858

08 A0 0F F0 0C 00

859

88 A8 8F E8 8C 83

JASSERT WRITE ENABLE & ERASE ENABLE

10 A0 0F 00 0C

85A

ICNTR FOR PREAMBLE BYTES

SE

00 A0 OF 80 D3 58

058

JLOOP TILL FIFO READY FOR MORE

05C

00 A0 OF F0 UC 00

FEED FIFO ANOTHER BYTE

25D

80 A0 PB BB BC OA

IDEC PREAMBLE BYTE CNTR

ØSE

00 00 0F 00 03 58

JITERATE TILL CHTR GOES TO 0

THE PREAMBLE IS NOW ON ITS WAY TO THE DISK (SOME OF IT IS STILL IN THE FIFO). NEXT WILL BE THE SYNC BIT FOLLOWED BY 2 MEADER BYTES.

05P

88 A0 0F 00 D3 5F

JWAIT FOR FIFO

866

00 A0 OF F0 OC 80

IDISPATCH SYNC BIT

95 AE OF 80 0C EO

861

JCLR ALL BUT CYLINDER BITS

845

88 A0 0F 80 D3 62

SWAIT FOR FIFO

863

11 00 00 FB 0C 00

JDISPATCH 1ST HEADER BYTE

864

95 AF OF 80 00 1F

JREMOVE DRIVE SEL BITS

```

```

065 00 A0 OF 80 D3 65

JWAIT FOR PIFO

866 11 88 88 FB 8C 98

FDISPATCH END HEADER BYTE

THE SYNC BIT & THE 2 BYTE HEADER ARE NOW ON THE WAY TO THE DISK.

NEXT COMES 512 BYTES OF DATA, BUT 1ST THE DISK WORD COUNT (DMC) IS UPDATED BY SUBTRACTING THE UNIBUS WORD COUNT (UWC).

25 E1 20 00 0C 00

067

# WRITE INNER LOOP

00 80 0F 04 F3 68

SINITIATE UNIBUS TRANSFER, WAIT FOR FIFO & UBUS

968

15 A4 48 F0 0C 00

JCOPY DATA TO FIFO & BUILD CHECKSUM

969

JBUMP MA. CARRY INTO HI CHECKSUM BYTE ?

00 80 OF 08 33 6C

06A

IYES, SO INC CHK1

0D E0 50 00 0C 00

268

INAIT FOR FIFO

00 A0 0F 00 03 0D

06C

ICOPY DATA & BUILD CHECKSUM

860

15 AS 5A FØ 9C 90

JUNIBUS HC EXHAUSTED ?

06E

60 E0 10 00 0C 00

00 BO OF 00 03 68

ING, THEN WRITE ANOTHER WORD TO DISK

06F

JDISK WC ALSO EXHAUSTED 7

070

10 42 00 00 00 00

00 B0 PF 00 03 B7

IND, THEN WRITE '0'S TILL IT IS

671

SIZ DATA BYTES ARE ON THE WAY TO THE DISK. NEXT COMES 2 CHECKSUM SYTES

AND THEN THE POSTAMBLE.

072

80 A0 PF 90 U3 72

JWAIT FOR FIFO

073

11 04 40 FØ 0C 00

INISPATCH LO CHK BYTE

074

00 Ag OF 00 D3 74

875

11 05 50 FØ UC 00

... & NOW HI CHK BYTE

1 POSTAMBLE

076

10 AT OF 00 UC 06

077

00 A9 NF 60 D3 77

JWAIT FOR FIFO

JOISPATCH A PIECE OF THE POSTAMBLE

078

00 AG OF FØ 8C 89

079

20 A0 00 00 0C 00

IMORE POSTAMBLE TO COME ?

IVES, SO ITERATE

07A

00 A0 OF 00 03 90

POSTAMBLE IS ON ITS WAY TO THE DISK. NOW WE MUST WAIT FOR FIFO TO

: EMPTY REFORE THE WRITE CURRENTS ARE DISABLED.

00 BU OF OO C3 79

978

JETFO DUTPUT REG EMPTY ?

IMAKE SURE WE DIDN'T SEE BETWEEN BYTE GLITCH

00 Be OF 00 C3 78

87C

"NXTSEC" WILL DISABLE THE WRITE OR READ CURRENTS AND CHECK IF MORE

DATA IS TO BE READ OR WRITTEN BEYOND THE SECTOR THAT HAS JUST BEEN

COMPLETED. IF MORE IS CALLED FOR, 'DOSEEK' WILL BE CALLED TO

POSITION THE HEADS FOR THE NEXT SECTOR & THEN CONTROL WILL BE RETURNED

TO THE READ OR WRITE ROUTINE.

IBUMP DA TO NEXT SECTOR, DISABLE CURRENTS

07D

DD EO EF EU OC OR

95 AE OF 00 OC OF

COPY JUST SECTOR TO RO

07E

JOVERFLOW TO NEXT TRACK ?

07F

34 EO OF DO MC OC

IND, THEN BO TO THORE!

080

88 80 0F 89 83 84

INEXT TRACK, SECTOR OF CARRY OUT OF REDACE ?

15 AE EF 00 UC 04

081

882

00 B0 0F 00 33 84

JYES, SO BUMP RXDA1 JANY MORE TO TRANSFER ?

00 E0 F0 80 0C 00

883

884

10 AB 00 00 0C 00

IND, THEN WE'RE ALL DONE

885

00 A0 0F 00 03 0A

INEED SEEK TO NEW CYLINDER ?

94 AE OF 80 0C 1F

886

ING, PRETEND SEEK JUST COMPLETED

90 80 0F 00 03 A4

687

*DOSEEK* IS THE ROUTINE THAT SEEKS TO THE CYLINDER ADDRESSED IN THE

INTERNAL RKDA. AFTER THE SEEK HAS BEEN COMPLETED, "GKSEEK" WILL WAIT UNTIL THE SPECIFIED SECTOR IS JUST BEFORE THE HEADS (SECTOR PULSE

IS SEEN) AND THEN RETURN TO THE CALLING ROUTINE.

JCOPY SECTOR BITS TO RO

988

95 AE OF OO OC OF

34 E0 OF 00 0C 0C

JLEGAL SECTOR NUMBER ?

889

88A

80 50 OF 01 13 10

IND, THEN TAKE ERROR EXIT

95 AE 6F 80 0C E0

JOOPY CYL BITS TO LO, HI

888

95 AF 7F 00 0C 1F

88C

10 86 00 00 00 00 00

880

ILOAD LOW CYL REG

```

```

08E 18 87 00 C0 00 00

08F 00 A0 0F E0 0C 08

# ... & HIGH CYL REG

OB AD OF ED OC OB

JINITIATE SEEK

THE SEEK HAS JUST BEEN INITIATED, NOW LOOP ON CHECKING FOR SEEK ERROR

OR SEEK DONE.

098 - 10 A0 02 00 0C 00

JGET ERROR BITS

691

99 AG OF EG OC OG

IDROP 'STBCYL'

892

00 50 0F 01 03 14

JIF ERR, GO TO 'UNSAFE'

693

10 AR P1 R0 0C 00

IREAD SECTOR COUNTER

094

95 AØ ØF ØØ ØC 4Ø

IBUSY SEEKING ?

095

88 80 0F 00 03 90

IYES, SO LOOP

SEEK COMPLETE. NOW READ HEADER OF NEXT SECTOR THAT COMES BY AND

VERIFY THAT THIS IS THE CORRECT CYLINDER, UNLESS THIS IS A

FORMAT READ IN WHICH CASE THERE IS NO CYLINDER VERIFICATION.

096

94 A9 OF OO OC 04

FORMAT READ ?

097

90 80 UF 90 93 A4

IYES, SO BYPASS VERIFICATION

298

00 B0 0F 00 A3 98

INAIT FOR SECTOR PULSE

099

10 AU OF 00 OC 80

JEDAD DELAY COUNTER

09A

40 A0 A0 A0 AC AU

TWAIT FOR PREAMBLE TO GET UNDER HEADS

098

00 BM OF 00 03 9A

IMAIT LOOP

00 40 00 50 0C 00

09C

PRESTORE FIFO REGISTERS

agn

00 A0 0F E0 0C 04

JASSERT READ ENABLE

99E

88 A8 8F 88 C3 9E

IMAIT FOR 1ST HEADER BYTE

09F

34 E6 0E 00 0C 00

FLOW CYL ADDR OK ?

00 80 0F 01 03 18

00 A0 0F 00 C3 A1

DAD

INO, THEN SEEK ERROR

0A1

IWAIT FOR END HEADER BYTE

34 E7 RE 00 0C 00

0A2

THIGH CYL ADDR OK ?

BAS

20 80 0F 01 03 18

IND, THEN SEEK ERROR

GOOD SEEK. NOW INITIALIZE CHECKSUM REGISTERS TO ZENO, SET UNIBUS WORD COUNT TO WHATEVER IT SHOULD BE, & SET DISK WORD COUNT FOR ONE

1

SECTOR (256 WORDS),

ØA4

89 A0 40 00 0C 00

ICLR CHECKSUM REGISTERS

ØAS

89 AB 50 80 80 00 BB

BAS

89 A0 20 00 0C 00

1256, WORD DISK TRANSFER

89 AP 10 00 00 00

8A7

1455UME ALL OF SECTOR WANTED

BAB

80 E8 88 88 8C NA

IFULL SECTOR TRANSFER ?

649

88 89 0F 00 03 AD

I'OKSEEK' IF HORE THAN FULL SECTOR

MAB

11 AA 10 00 0C 00

ISET UNIBUS WORD COUNT

BAR

89 A0 A0 00 0C 00

ICLR INTERNAL REWC (LAST SECTOR)

# SELECT HEAD

0AC 00 A0 0F 00 81 82

AT "OKSEEK", EVERYTHING IS SET UP FOR THE UPCOMING TRANSFER. NOW

THE CONTROLLER WILL WAIT UNTIL THE SPECIFIED SECTOR IS JUST REACHING

THE HEADS REFORE RETURNING TO THE CALLER.

89 B0 0F 00 A3 AD

ØAD

JWAIT FOR SECTOR PULSE

BAE

D4 AE 01 00 00 00

ISPECIFIED SECTOR ?

94 A8 OF 00 0C OF

GAF

JOON'T KNOW TILL WE CLEAN IT UP

68 BØ OF 00 03 AO

686

INDT SECTOR WE WANT

881

86 A6 0F 60 8A 00

IRETURN

"SELECT" SELECTS THE HEAD SPECIFIED IN THE INTERNAL REDA.

982

95 AE 6F 00 0C 10

JCOPY HEAD SEL BIT TO "LO"

883

10 86 00 00 00 00

ISELECT HEAD

984

22 AS OF PO SA GO

JRETURN

"HRITEZ" APPENDS ZEROS TO SHORT RECORDS AS THEY ARE WRITTEN ON

THE DISK.

085

80 E0 20 00 0C 00

JMARK PASSAGE OF ANOTHER WORD TO DISK

ØB6

88 AR OF BU 03 72

J'WRTDON' WHEN DONE

Ø87

00 AM WF 89 03 87

IWAIT FOR FIFO

88 AR OF FR OC 00

988

JOISPATCH A ZERO

```

ېد

889

00 AR PF BB D3 89

```

00 AN OF FO OC ON

IPAD

384

088 00 AQ OF 00 02 85

JLOOP

# READ OPERATIONS == READ, READ CHECK, & WRITE CHECK ALL TRANSFER HERE.

94 80 0F 30 0C 32

ISET A17, A14, C1, & C0

08C

00 A0 0F 00 61 88

06D

LOAD DELAY COUNTER

10 A0 0F 00 0C 80

68E

SWAIT FOR PREAMBLE TO GET UNDER HEADS

ØBF

20 40 00 00 00 00

JHAIT LOUP

BCB

00 80 OF 00 03 BF

ØC1

88 AB 88 50 90 88

IRESTORE FIFO REGISTERS

JASSERT READ ENABLE

0¢2

00 A0 OF E0 OC 04

IWAIT FOR 1ST HEADER BYTE

00 A0 OF 90 C3 C3

ØC3

10 AP 6E 90 0C NO

IGET 187 HEADER BYTE

ØC4

IWAIT FOR END HEADER BYTE

00 A0 OF 00 C3 C5

005

. .. & STICK IT IN "HI"

ØC6

10 AU 7E 00 0C 00

94 A9 OF UD OC 04

FORMAT READ ?

0C7

TYES, SO TRANSFER JUST HEADER BYTES

00 80 MF 00 03 F6

ØC8

FREAD OR WRITE CHECK ?

94 A8 OF BO UC 92

6C9

00 80 OF 00 03 DF

OCA

IYES

JUPDATE, DISK WORD COUNT

0CB

25 E1 20 00 0C 00

# DISK READ INNER LOUP

SWAIT FOR DATA

9CC

00 A0 OF 00 C3 CC

ICOPY DATA & BUILD CHECKSUM

ØCD

15 A4 4E 40 0C 00

FBUMP HA. CARRY INTO CHK1 ?

ØĈĒ

00 80 0F 08 33 Do

TYES, SO SEE THAT IT GETS THERE THAT FOR DATA & UNIBUS

OCF

00 E0 50 00 0C 00

000

00 80 NF 00 E3 D0

ICOPY & BUILD

901

13 AS SE 50 MC 00

ISTART UNITEDS TRANSFER. THIS LAST WORD ?

902

00 E0 10 04 0C 00

0D3

00 80 0F 00 03 CC

ØD4

10 A2 00 00 0C 00

IMORE DATA STILL IN SECTOR ?

IYES, SO CONT TO BUILD CHECKSUM

805

00 80 0F 00 03 E1

DATA HAS JUST BEEN READ. NOW READ & VERIFY CHECKSUM.

406

IWAIT FOR 1ST CHECKSUM BYTE

00 AB 0F 00 C3 06

807

35 E4 4E 88 8C 88

JOUR LOW CHECKSUM BYTES

IDON'T FORGET THE CARRY

800

00 60 OF 00 33 DA

-009

20 A0 50 00 0C 00

FOK

00A

00 A0 0F 00 C3 DA

JWAIT FOR 2ND CHECKSUM BYTE

0D8

35. E5 5E 90 UC 00

ISUB HIGH CHECKSUM BYTES

JCHECKSUM ERROR ? DISABLE READ CURRENT

ODC

64 A4 SF E0 0C 00

INO, THEN ERROR

00D

00 B0 OF 01 03 GE

FIF MORE, CONT TO NEXT SECTOR

00 A0 0F 00 02 7D

BOE

READ & WRITE CHECK TRANSFER TO "RDCKO". NOW TEST TO SEE WHICH IT

IS AND BRANCH ACCORDINGLY.

OOF

94 AS OF DO OC U4

FREAD CHECK T

INO, SO MUST BE WRITE CHECK

0E0 00 80 0F 00 03 EA

J READ CHECK INNER LOOP

IWAIT FOR DATA

ØEt

00 A0 0F 00 C3 E1

0E2

15 A4 4E 00 0C 00

IBUILD CHECKSUM

OE3

00 BO OF OO 33 E5

ICARRY ?

80 E8 58 88 8C 88

0€4

IYES

IWAIT FOR DATA

ØE5

00 A0 PF 00 C3 E5

15 A5 5E 00 0C 00

IBIJILD CHECKSUM

SEA

0E7

80 E8 28 88 8C 88

IBUMP DISK WORD COUNT

JLOOP THRU ALL OF SECTOR

ØE8

00 BU OF OU US E1

. .. & THEN GO TO PRODONE

ØE9

00 40 0F 00 02 06

# WRITE CHECK INNER LOOP

ØEA

00 A0 00 04 0C 00

ISTART UNIBUS READ

00 A0 OF 00 03 40

INAIT FOR DATUM FROM BOTH SOURCES

ØEB

ØEC

1D AØ 6E ØØ ØC ØØ

JGET DISK DATA BYTE

ØED

34 E6 0B 00 0C 00

JSUB BYTE FROM HEMORY

ØEE

00 80 0F 01 03 0C

JERROR IF NOT 0

0EF

10 40 64 00 0C 80

JGET BYTE FROM MEMORY

```

```

0 F Ø

00 A0 0F 00 C3 F0

JWAIT FOR DISK DATA

0F1

34 E6 DE 00 DC 00

$8UB BYTE FROM DISK

00 80 0F 01 03 0C

0F2

JERROR IF NOT W

OF3

90 EØ 10 00 0C 00

JAUMP UNIBUS WORD CHT

ØF4

00 80 0F 00 03 EA

JLOOP TILL DONE

OF5

00 A0 OF OO 02 FA

JOIN FORMAT READ STREAM

FORMAT READ == THE 2 HEADER BYTES ARE IN "LO" & "HI".

TRANSPER THEM

TO MAIN MEMORY & ITERATE TILL UNIBUS WORD COUNT IS 0.

0F6

11 E1 A0 00 0C 00

SINTERNAL REWC NEEDS UPDATE

0 F 7

00 A0 OF 00 63 F9

OFS

2D AØ BØ ØØ ØC ØØ

JUNDO WHAT "SEEKOK" DID

00 AO OF 01 81 07

0F9

STRANSFER HEADER

ØFA

00 A0 0F 00 81 70

JIF MORE, CONT TO NEXT SECTOR

OFB

00 A0 0F 00 02 BE

IREENTER READ STREAM

SFEK ROUTINE -- SINCE SEVERAL REMS DRIVES ARE MAPPED ONTO THE PERTEC

DRIVE, IT IS REST TO SEEK ONLY BEFORE PERFORMING A DATA TRANSFER.

ØFC

75 A9 9F 00 0C 20

ISET "SEARCH COMPLETE" IN RKCS

OFO 00 A0 0F 00 02 0A

INE RE DONE 1

DRIVE RESET -- RECALIBRATE & BRANCH TO "SEEK"

ØFE

00 A0 0P 01 81 28

IRECALIBRATE

00 A0 0F 00 02 FC

9 F F

JOIN UP WITH PSEEK

J UNIBUS DATA TRANSFER SUBROUTINES

100

90 AN OF 30 UC 30

SINITIAL DATA IN ENTRY POINT

INITIATE TRANSFER

101

88 AB 88 84 8C 88

102

00 BO OF 01 63 02

JWAIT FOR UNIOUS

103

1D A0 6B 00 0C 00

JGET LOW DATA BYTE

104

10 A0 7A 90 0C 00

1 ... & HIGH DATA SYTE

105

00 A0 OF 08 8A 00

#RETURN

106

00 A0 0F 30 AC 32

FINITIAL DATA OUT ENTRY POINT

107

10 86 00 40 00 00

JCOPY LOW DATA

10 87 00 50 00 00

108

I ... B HIGH DATA

80 A0 00 04 0C 00

88 B0 0F 81 63 0A

INITIATE TRANSFER

109

12A

FHAIT FOR TTRANSFER DONES

88 AO OF OB BA OO

108

IRETURN

ERROR ROUTINES -- ALL ERRORS ARE HANDLED IN THE SAME MANNER.

. 1ST THE APPROPRIATE ERROR BIT IS SET IN THE INTERNAL ERROR REGISTER

(RM, UMC), AND THEN THE INTERNAL RKCS IS CHECKED TO SEE IF STOP ON SOFT ERROR' IS SET. IP NOT, THEN 'RETRY' WILL BE CALLED TO ATTEMPT THE COMPLETE TRANSFER ONCE AGAIN. UP TO 16 RETRIES WILL

BE ATTEMPTED AUTOMATICALLY. IF THE ERROR CONDITION PERSISTS, OR *STOP ON SOFT ERROR* IS SET, THE EXTERNAL REER WILL BE READ AND ORED

WITH THE INTERNAL ERROR REGISTER & THEN THE EXTERNAL RKER WILL BE

UPDATED WITH THIS NEW EHROR DATA. FINALLY, THE EXTERNAL RKCS WILL

BE UPDATED WITH THE APPHOPRIATE ERROR SITS & CONTROL WILL TRANSFER

TO "UNNE".

100 10 A0 OF 80 00 01

ISET "WCE" IN RKERO

10D

00 A0 OF 01 02 13

10E

10 AM OF 00 0C 02

ISET "CSE" IN RKERS

107

00 A0 OF 01 02 13

110

10 AM OF 00 MC 20

ISET 'NYS' IN PRERO

111

00 A0 OF 01 02 13

112

10 AØ ØF ØØ ØC 4Ø

ISET 'NXC' IN RKERO

89 AO 1F O1 O2 1A

113

ICLR RKERI. GO TO 'ERROR'

114

94 40 07 00 00 02

JSEEK INCOMPLETE ?

115

00 80 0F 01 03 12

FYES, THEN PRETEND "NXC"

1D A0 1F 00 0C 80

116

```

00 A0 OF 01 02 19

117

118 1D AØ 1F ØØ ØC 10 ISET "SKE" IN RKER1 119 89 AM OM 00 OC OM ICLR RKERO 94 49 0F 00 UC 01 IIA ISTOP ON SOFT ERROR ? 89 B0 0F 01 03 1E 118 JYE8 20 A0 30 00 00 00 80 B0 0F 01 03 29 110 DEC ERR CHTR. TIME TO GIVE UP 1 110 ING, SO TRY AGAIN ISET MA # 177402 (RKER) 00 A0 0F 60 0C 02 11E 117 00 A0 OF 70 0C PF 20 AN OF 01 81 00 120 TREAD EXTERNAL RKER 121 65 AO 60 DO OC OD SUPDATE OLD RKER 155 65 A1 7F 60 0C 02 IRESET MA TO 177402 153 80 A0 OF 01 81 06 INRITE UPDATED RKER 75 A9 9F 00 0C 80 124 ISET 'ERROR' IN RKCS! 125 94 AØ OF 80 OC 03 ISOFT ERROR T 126 00 80 OF 00 03 0A 1YES 127 75 A9 9F 80 0C 40 JNO, SO SET "HE" IN RKCS1 128 80 A0 OF 80 02 0A FRETURN IN DISGRACE 129 00 A0 0F 01 81 28 PRECALIBRATE 00 AD OF DO 02 1F 184 7 44 & TRY AGAIN 128 00 A0 DF C0 00 40 JASSERT 'RESTORE! 12C 88 A0 OF E0 OC 08 JASSERT 'STECYL" 88 A8 88 80 8C 88 150 1 PAUSE 88 AB OF ED OC 88 12E FREMOVE 'STBCYL' 10 A0 01 00 0C 00 127 ILOOP TILL NOT "BUSY" 135 00 AD OF 01 03 2F 131 JYE8 132 00 A0 OF 00 SA 00

JEXIT