### SECTION VI

### PROGRAMMING EXERCISES

### INTRODUCTION

The Am2900 Evaluation and Learning Kit is intended to teach the basics of microprogramming to the hardware design engineer. The exercises are geared to the objectives of demonstrating the uses of the Am2901 and Am2909 and to involve the user in the microprogramming of these devices. In addition, it is intended to allow evaluation of the Am2901 and Am2909 in an application environment. As such, the learning exercises are divided into two sections. These include static exercises and dynamic exer-The static exercises are performed using the toggle switches and momentary switches available on the printed circuit board. user clocks the system by hand observing the various states of the machine at each point. The dynamic tests are set up using the switches on the printed circuit board but are evaluated by using an external pulse generator and oscilloscope. This allows the Am2901 and Am2909 to be tested under operating conditions. fashion, the student can learn microprogramming techniques in the SINGLE STEP CLOCK mode and can evaluate the components in the PULSE GENERATOR mode, bearing in mind that the kit has not been designed as a small computer. However, once the user understands the Am2901, Am2909 and the principles of microprogramming, then the design of a computer becomes obvious.

The static test exercises are divided into three basic groups. The first group is intended to familiarize the engineer with the Am2901 capabilities. The second group is intended to familiarize the engineer with the Am2909 functions. The third group of exercises that can be generated appear almost infinite. The exercises presented here are only representative and the student is encouraged to write numerous additional exercises to evaluate any specific parameter or feature in which he is interested.

In the dynamic testing mode, several exercises are presented such that the student can evaluate typical switching characteristics. Many of the specified parameters of the Am2901, Am2907, Am2909 and Am2918 can indeed be measured using the Am2900 Kit. It is not possible to measure some of the parameters due to the complex nature of the testing required.

### USING THE EXERCISES

The microprogramming exercises are contained on the Am2900 Kit microprogramming worksheets following this discussion. These worksheets show the specific "logic one" and "logic zero" codes that must be entered into the microprogram memory in order to execute the various microinstructions so as to perform a function (HIGH = logic one). The results of the execution of these micro-

instructions is described in the accompanying text.

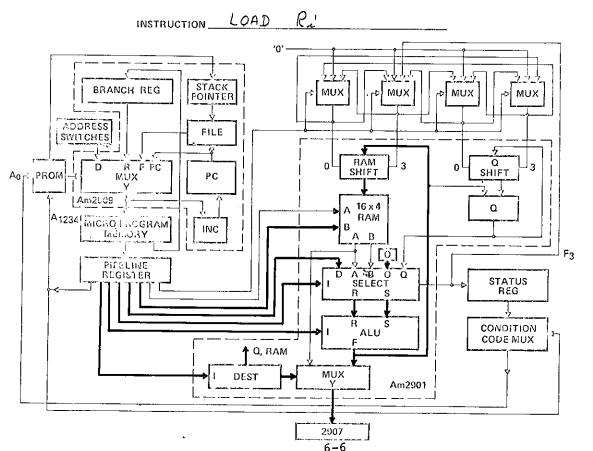

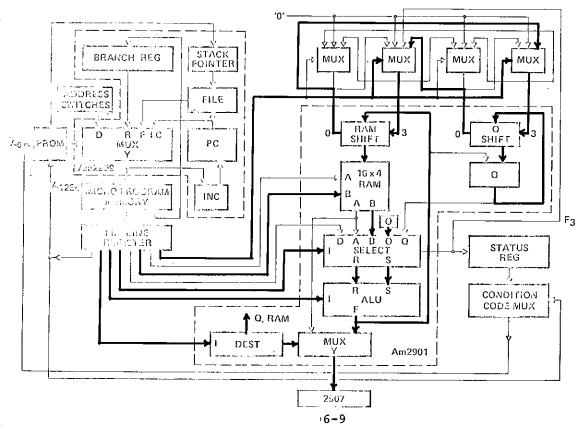

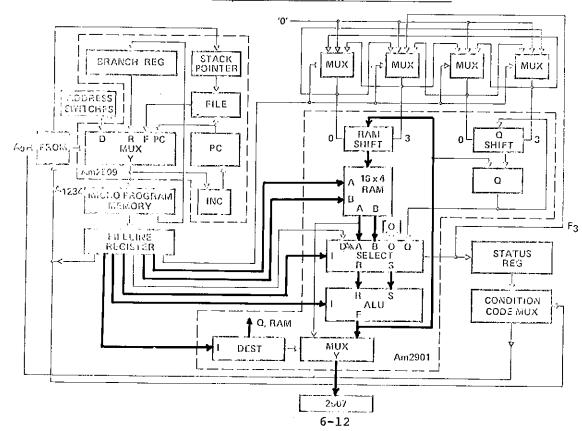

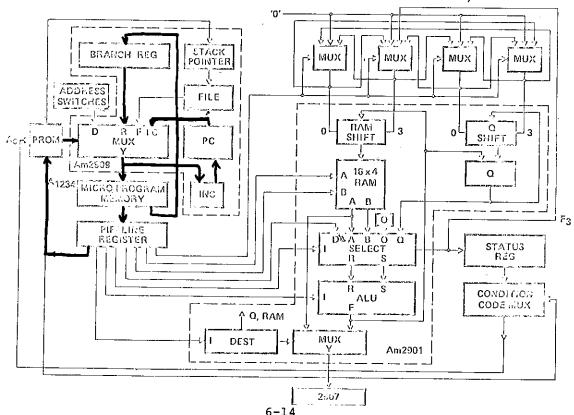

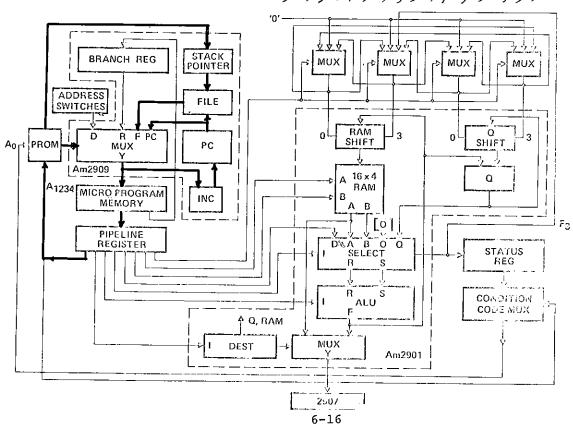

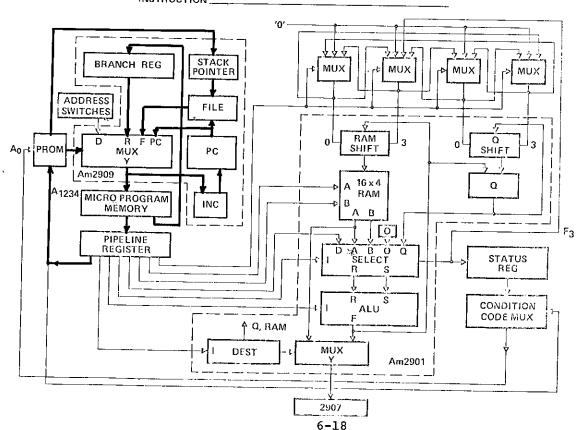

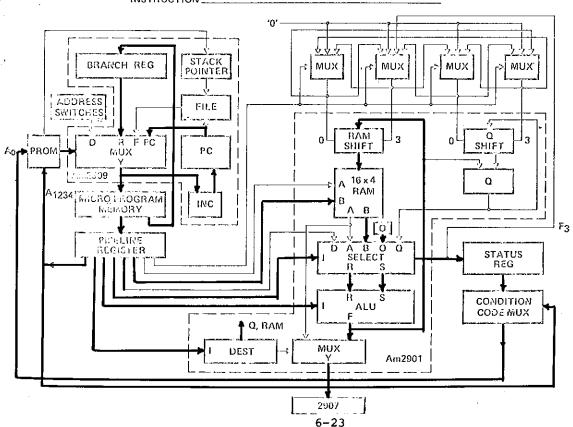

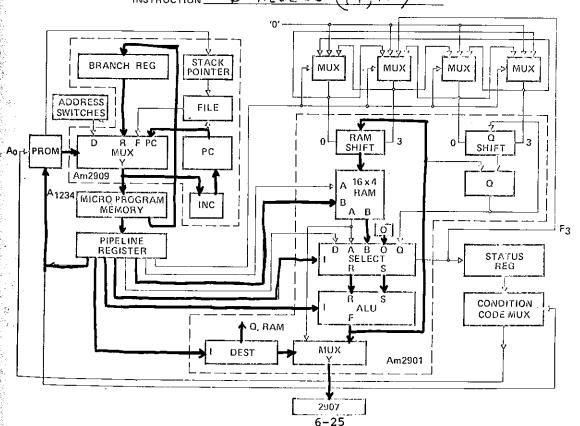

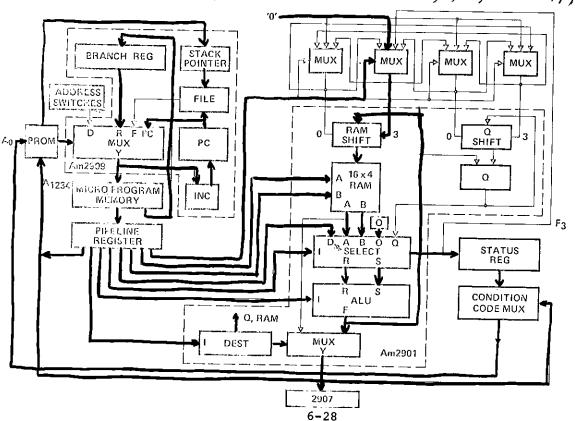

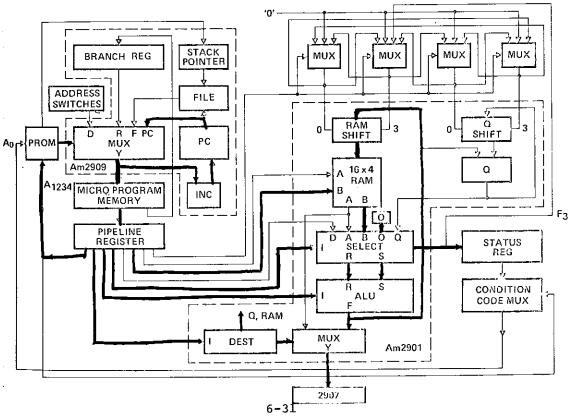

The Am2900 Kit programming worksheet is divided into two main parts. The top half of the worksheet shows a map of the entire 16-word by 32-bit microprogram memory. The logic ones and logic zeros associated with the fields of each microprogram memory word can be entered into the worksheet. Any blank space on the worksheet indicates a "don't care" condition. The bottom half of the worksheet shows a functional block diagram representation of the Am2900 Kit. This block diagram is intended to allow the user to sketch the path of a microinstruction so he may more easily understand the actual event being executed. The use of these two sections of the worksheet is demonstrated in the exercises.

### PROGRAMMING THE MICROPROGRAM MEMORY

The recommended procedure for using the exercises as described with the Am2900 Kit is to load all the required data into the microprogram memory. For example, all six words of Exercise 1 should be loaded into the microprogram memory before executing these instructions. The procedure to be used in loading the microprogram memory is as follows:

- Connect the 5V power supply to the Am2900 Kit and apply power.

- 2. Set the RUN/LOAD SELECT switch (S12) to the LOAD position.

- 3. Set the MEMORY ADDRESS switches (S8-S11) to the decimal zero position.

- 4. Set the RAM & MUX SELECT switches (S1-S3) to the decimal zero position.

- 5. Set the MEMORY DATA switches (S4-S7) to the required bit position.

- 6. Depress the MEMORY LOAD switch (S14) to enter the data.

- 7. View the MICROWORD MEMORY LED's to be sure the correct word has been written into the microprogram memory.

- Repeat steps 3-7 for each decimal position of the RAM & MUX SELECT switches until all eight fields (decimal 0-7) have been loaded.

- 9. Repeat steps 3-8 for each microprogram memory address word until the entire 16 words (word 0-15) of the microprogram memory have been loaded.

Needless to say, any blank entries ("don't care" conditions) may be omitted. When this procedure is followed, all possible 128 four-bit fields in the microprogram memory are easily loaded.

The above description has sequentially loaded the 8 four-bit fields of the microprogram word, one word at a time. The user may wish to load all 16 words of each field sequentially. That is, the RAM & MUX SELECT switches are set to decimal 0 and each MEMORY ADDRESS is loaded with the appropriate word for the entire 16 words of the memory. Advanced Micro Devices' Applications Engineers have found both techniques to be convenient depending on the particular exercise.

Once the microprogram memory has been loaded, the exercise should be executed as described in the accompanying text with the programming worksheet.

### CONNECTING THE PULSE GENERATOR

The Am2900 Evaluation and Learning Kit is designed such that it can be easily driven from a pulse generator. Two turret terminals are provided near resistor R9 so that a coaxial cable can be soldered to the board. One of the turret terminals is marked "GND" and connects directly to the ground bus of the system. A 51 ohm resistor is connected directly between the two turret terminals. This provides a termination for the coaxial cable at the U29 IC so that the cable is properly matched.

The printed circuit board has been designed such that it will accept a printed circuit type BNC connector. If the user desires, he may purchase a King's KC-79-153 connector for installation directly beneath the pulse generator turnet terminals. This will provide a second method for connecting the pulse generator to the Am2900 Evaluation and Learning Kit. In some laboratory environments, this may be more convenient than directly connecting a coaxial cable to the printed circuit board.

### Programming Exercise #1 - Loading the Am2901 Memory

Many of the operations performed with the Am2901 Microprocessor will involve the use of the 16-word, two-address RAM. These 16 RAM locations may be employed at the option of the user as program counters, accumulators, index registers, scratch pad memory, stack pointers, non-user registers, and so forth. Application of the RAM can be determined by the system architecture as well as the microprograms. The purpose of this exercise is to demonstrate one technique for loading the 16 registers from the incoming data input. The exercise is written so as to load a selected word in the RAM memory and then advance to the next line of microprogram code. At this word, the contents of the Am2901 RAM is read out so that it can be examined at the output of the Am2901.

In this exercise, microprogram word zero contains a microinstruction that will load Register "0" of the Am2901 with the value

binary two. The microinstruction at word one in the microprogram

memory reads the contents of register zero to the Am2901 output

via the B data output of the 16 x 4 RAM. Microinstructions 2 and 3

perform the same function on RAM Register "1" while microinstructions

4 and 5 perform the same function on RAM Register "9". Obviously,

the user can load and examine all 16 registers in the Am2901 RAM using

a similar pair of microinstructions. Incidentally, microinstructions

0 and 1 could be used to perform this function on all 16 registers

in the Am2901 by simply re-loading the contents of the microprogram

memory "D" and "B" fields and then executing these two instructions;

then reloading and executing again.

The actual execution of this exercise is as described below. Leave the RUN/LOAD switch in the LOAD position and set the MEMORY ADDRESS switches to decimal 0. First, depress the SINGLE STEP CLOCK momentary switch so as to enter the contents of the microprogram memory into the pipeline register. Next, advance the MEMORY ADDRESS switches to the decimal 1 position and again depress the SINGLE STEP CLOCK momentary switch. This has the effect of executing the contents of the pipeline register which is currently word zero and entering the contents of microprogram memory word 1 into the pipeline register. The result is that binary two is loaded into Register 0 and the pipeline register contains an instruction that is currently reading the contents of Register 0 to the Am2901 outputs. The user can view the Am2901 outputs on the DATA DISPLAY LED's by setting the RAM & MUX SELECT switches to the decimal 1 position. When this function is performed, the DATA DISPLAY reads binary two (0010).

The next pair of microinstructions which load Register 1 can be executed in a similar fashion. That is, set the MEMORY ADDRESS select switches to the decimal 2 position and depress the SINGLE STEP CLOCK momentary switch. This loads the contents of microprogram memory word 2 into the pipeline register. Next, advance the MEMORY ADDRESS switches to the decimal 3 position and again depress the SINGLE STEP CLOCK momentary switch. This executes the contents of the pipeline register and enters the "read" microinstruction into

the pipeline register. Thus, the user now views the word that has been loaded into Register 1 of the Am2901 RAM. Microinstruction words 4 and 5 are executed in a similar fashion.

The purpose of this exercise is to demonstrate the simple loading of data into the Am2901 memory. The loading of the Q register can be accomplished in exactly the same fashion with only the destination select field of the microinstruction control word being changed. In this example, each "load" instruction has been followed by a "read" instruction so the contents of the Am2901 memory can be examined. In normal operation, only the load operation is performed and the machine moves on to the next task at hand.

EXERCISE NUMBER:

NAME: LOADING THE AM 2901 RAM

### MICROPROGRAM MEMORY

| HAM &   | 7                                               | 6                               |           | 5                                       |          | 4            |            | Τ              |    | 3   |    | 2           |    | 1          | Γ | 0                                            | N               | OTES         |

|---------|-------------------------------------------------|---------------------------------|-----------|-----------------------------------------|----------|--------------|------------|----------------|----|-----|----|-------------|----|------------|---|----------------------------------------------|-----------------|--------------|

| MEMORY  | BRANCH<br>ADDRESS                               | MEXT<br>MINSTHUCTION<br>CONTROL | MUX1      | OEST.<br>SELECT                         | MUXO     | SEL          | BCE<br>LCT | C <sub>n</sub> | ]  | ALU |    | 'A'         | ļ_ | 'B'        |   | .0.                                          | NEXT<br>AUDRESS | DATA         |

| ADDAESS | Bu <sup>3</sup> Bu <sup>4</sup> Bu <sup>9</sup> | P3 F2 F1 P0                     | -         | 1 "   " " " " " " " " " " " " " " " " " | 2        | 12           | '1 10      | <u> </u>       | 15 | غنا | 13 | A3 A2 A1 A0 |    |            |   | D <sub>2</sub> D <sub>1</sub> D <sub>0</sub> | CONTROL         |              |

|         |                                                 | <u> </u>                        | _         | 011                                     | _        | <u> </u>     | <u> </u>   | _              | 0  | 1   | 1  |             | 0  | <u>000</u> | 0 | 010                                          |                 | LOAD Ro      |

| 1       |                                                 |                                 | _         | 001                                     | _        | 0            | <u> </u>   |                | 0  | 1   | ı  |             | 0  | 000        |   |                                              |                 | READ RO      |

| 2       |                                                 |                                 |           | 011                                     |          |              | 1 1        |                | 0  | 1   | 1  |             | 0  | 001        | 0 | 100                                          |                 | LOAD R,      |

| 3       |                                                 |                                 |           | 001                                     |          | 0            | 1 1        |                | 0  | 1   | Ī  |             | 0  | 001        |   |                                              |                 | READ RI      |

| 4       |                                                 |                                 |           | 011                                     |          | 1            | 1          | _              | 0  |     | I  |             | ī  | 001        | o | 101                                          |                 | LOAD RG      |

| 5       |                                                 |                                 |           | 001                                     |          | 0            | ī          | 1              | 0  |     | I  |             |    | 001        |   |                                              |                 | READ RO      |

| 6       |                                                 |                                 |           |                                         |          |              |            | 1              |    |     |    |             |    |            |   |                                              |                 | 1            |

| 7       |                                                 |                                 |           |                                         |          |              |            | Γ              |    |     |    |             |    | •          | _ |                                              |                 | -            |

| В       |                                                 |                                 | _         |                                         |          |              |            | T              | -  |     | -  |             |    |            |   |                                              |                 |              |

| 9       |                                                 |                                 |           |                                         |          |              |            | -              |    |     | 7  |             |    |            |   |                                              |                 |              |

| 10      |                                                 |                                 |           |                                         |          |              |            | -              |    |     | -  |             | _  |            | _ |                                              |                 |              |

| 11      |                                                 |                                 |           |                                         |          |              |            | -              |    |     | -  |             |    |            |   |                                              | <del></del> -   | 1            |

| 12      |                                                 |                                 | 7         |                                         | -        |              |            | -              |    |     | -  |             |    |            |   |                                              |                 | <del> </del> |

| 13      | _                                               |                                 |           |                                         | -        |              |            | -              |    |     | 7  |             |    |            |   |                                              |                 |              |

| 14      |                                                 |                                 | <b>-!</b> |                                         | $\dashv$ |              |            | -              |    |     | -  |             |    |            | _ |                                              |                 | 1            |

| 15      |                                                 |                                 |           |                                         | $\dashv$ | <del>-</del> |            | $\vdash$       |    |     | -1 |             |    |            |   |                                              | ·               | -            |

BLANK - DON'T CARE

### Programming Exercise #2 - Rotate Functions in the Am2901

The Am2900 Evaluation Kit is designed to provide four different shift matrix multiplexer control functions as shown on page 3-9 of the operational description. These four functions are enter zeros, rotate, double length rotate, and double length arithmetic rotate. This shift function can be performed in either the shift-up mode or shift-down mode. The purpose of this exercise is to demonstrate the use of the single length rotate up and down, as well as the double length rotate up and down.

First, the microprogram memory should be loaded with the various data as shown in the accompanying worksheet. Microprogram word 0 is used to load a binary one in the second bit position of Register 0 in the Am2901 RAM. The microinstruction at word 1 performs a rotate up function on this bit. Microprogram memory word 2 performs the rotate down function; word 3 is the double length rotate up function and word 4 is the double length rotate down function. Word 5 is shown to demonstrate the "no op" function.

Exercise 2 should be performed in the following manner. Keep the RUN/LOAD switch in the LOAD position. Set the MEMORY ADDRESS switches to the decimal 0 position and depress the SINGLE STEP CLOCK momentary switch. This will enter the contents of microprogram memory word 0 into the pipeline register. Next, advance the MEMORY ADDRESS switches to the decimal 1 positon. Depress the SINGLE STEP CLOCK momentary switch. If the RAM & MUX SELECT switches are set to the decimal 1 position, the output of the Am2901 Microprocessor will be viewed on the DATA DISPLAY LED's. The current contents of the DATA DISPLAY should be binary two (0010). Now, if the MEMORY ADDRESS switches are left at the decimal 1 positon and the SINGLE STEP CLOCK momentary switch is repeatedly depressed, the bit as displayed on the DATA DISPLAY will be rotated in the upward position. That is, the bit will move in the 2, 4, 8, 1, 2, etc. pattern (0010, 0100, 1000, 0001, 0010, etc.). As many times as the SINGLE STEP CLOCK momentary switch is depressed, the single length rotate up function will be executed.

Next, set the MEMORY ADDRESS switches to the decimal 0 position and depress the SINGLE STEP CLOCK momentary switch. This will again load the contents of microprogram memory word 0 into the pipeline register. Then, set the MEMORY ADDRESS switches to the decimal 2 position and depress the SINGLE STEP CLOCK momentary switch. This will execute the load two microinstruction and enter microprogram memory word 2 into the pipeline register. Now, with the RAM & MUX SELECT switches in the decimal 2 position, the DATA DISPLAY LED's will again show binary two (0010). Keeping the MEMORY ADDRESS switches in the decimal 2 position, each depression of the SINGLE STEP CLOCK momentary switch will result in the execution of a rotate down microinstruction. The pattern on the DATA DISPLAY will follow a 2, 1, 8, 4, 2, etc. sequence as the SINGLE STEP CLOCK momentary switch is depressed.

EXERCISE NUMBER:

BLAYE DUN LEARE

ود

NAME: ROTATE EXERCISES

#### MICROPROGRAM MEMORY

| RAM &<br>MUX                    | ,                                  | 6           | 5                              | - 4           | 3                                | 2               | 1                                                                 | 0    | NOTES .                   |

|---------------------------------|------------------------------------|-------------|--------------------------------|---------------|----------------------------------|-----------------|-------------------------------------------------------------------|------|---------------------------|

| AN MOTELY<br>ADDITESS           | BRANCA<br>ADI BIES<br>BIJER-BIJERS | P3 P2 P1 P0 | 5   SI (LCT   5   Ig   17   I6 | Source Series | ALU<br>C <sub>n</sub> - 15 14 13 | A3 A2 A1 A6     | u <sub>3</sub>   a <sub>2</sub>   u <sub>1</sub>   u <sub>0</sub> | 0.   | NEXT DATA ADDRESS CONTROL |

| 0                               |                                    | ·           | 011                            |               | 011                              |                 | 0000                                                              | 0010 | LOAD Ro                   |

| 1                               |                                    |             | 0.111                          | TOTI          | 011                              |                 | 0000                                                              |      | ROT UP                    |

| 2                               |                                    | i—          | oioi                           | 1011          | OII                              | - <del></del> - | 0000                                                              |      | ROT DN                    |

| 3                               | i                                  |             | 000                            | 010           | 100                              |                 | <u> </u>                                                          |      | CIK Q                     |

|                                 |                                    | ~           | 1110                           | 0011          | 011                              |                 | 0000                                                              | ·    | D&L ROTUP                 |

| · · · · · · · · · · · · · · · · |                                    |             | 1 100                          | 011           | 011                              | - <b></b>       | 0000                                                              |      | DBL ROTON                 |

| 7                               |                                    |             | 00.1                           |               | ונט                              |                 |                                                                   |      | No 00                     |

| B                               |                                    |             | <u> </u>                       |               |                                  |                 | ·                                                                 |      |                           |

| 9                               |                                    |             | :                              | -             | -                                | · ·             |                                                                   |      |                           |

| 10                              |                                    |             |                                |               |                                  |                 |                                                                   | ·    |                           |

| 11                              |                                    |             |                                |               |                                  |                 |                                                                   |      |                           |

| 12                              |                                    |             |                                | _             |                                  |                 |                                                                   |      |                           |

| 13                              |                                    |             |                                |               | _                                |                 |                                                                   |      |                           |

| 14                              |                                    |             |                                | i             |                                  |                 |                                                                   |      |                           |

| 115                             |                                    |             |                                |               |                                  |                 | i                                                                 | 1    | 1                         |

# INSTRUCTION DOUBLE LENGTH ROTATE DOWN

The double length rotate up and double length rotate down instructions are executed in a similar fashion. First, execute the word at decimal 0 position, then execute the word at the decimal 3 position and then execute the word at the decimal 4 or decimal 5 position. The word at the decimal 3 position simply performs a clear Q function so that the contents of the Q register intially is all zeros. The double length rotate up pattern will now be 2, 4, 8, 0, 0, 0, 0, 1, 2, 4, 8, 0, etc. Likewide, the double length rotate down pattern will be 2, 1, 0, 0, 0, 0, 8, 4, 2, 1, 0, etc.

The "no-operation" function at microprogram memory word 6, if selected, simply demonstrates that the Am2901 can be clocked with no write operation being performed. During any of the above exercises, the MEMORY ADDRESS switches can be changed to the decimal 6 position and the SINGLE STEP CLOCK momentary switch depressed. The result is that the no-operation function will be entered into the pipeline register and then executed. It should be remembered that when the MEMORY ADDRESS switches are changed to the decimal 6 position, the pipeline register will currently contain a rotate instruction. This instruction will be executed as the contents of the microprogram memory (no-operation) are loaded into the pipeline register. Thus, one additional execution of the rotate function takes place before the no operation instruction is executed.

The purpose of this exercise is to demonstrate how an external multiplexer can be used to perform single length and double length rotates in either direction. The user is encouraged to write instructions that perform shifting of zeros into the word and double length arithmetic shifts. From this example, it should be apparent to the user that a multiplexer scheme can be designed to include the carry flip-flop such that single length and double length rotate with or without carry could be implemented. Likewise, shifting ones or shifting zeros into the Am2901 would be possible.

## Programing Exercise #3 - Am2901 Arithmetic Operation

The purpose of this exercise is to demonstrate a small set of the arithmetic capability of the Am2901 Microprocessor. Four different instruction types are demonstrated on the worksheet for this exercise. The first three types are demonstrated in microprogram memory words 0, 1, and 2 while the fourth type is demonstrated using three microinstructions at memory locations 7, 8, and 9. Again, all data shown in the worksheet should be entered into the microprogram memory.

This exercise is executed in the following manner. Set the RUN/LOAD switch to the LOAD position and set the MEMORY ADDRESS switches to the decimal 0 position. If the RAM & MUX SELECT switches are set to the decimal 1 position, the output of the Am2901 Microprocessor can be viewed on the DATA DISPLAY LED's. Each time the SINGLE STEP CLOCK momentary switch is depressed, the current DATA DISPLAY will be incremented by one.

This is accomplished by using the B and O source operands, adding in the ALU with the carry-in set to a one, and writing the results into the Register O of the RAM.

If the MEMORY ADDRESS switches are placed in the decimal 1 position, each time the SINGLE STEP CLOCK momentary switch is depressed, the contents of Register 0 will be decremented. Thus, the DATA DISPLAY will show this decrement function on the contents of Register 0.

If the MEMORY ADDRESS switches are placed at the decimal 2 position, each depression of the SINGLE STEP CLOCK momentary switch will result in the contents of Register 0 being increased by three. Needless to say, an overflow will occur every six clock cycles and the contents of the register will "end around" from a positive value to a negative value. This microinstruction demonstrates adding a data bus input value on the D inputs to the contents of a register.

Microinstruction words 7 and 8 perform the required set-up to demonstrate a register-to-register add operation at microinstruction word 9. This sequence of microinstructions is executed in the following manner. Set the MEMORY ADDRESS switches to the decimal 7 position and depress the SINGLE STEP CLOCK momentary switch. Next, set the MEMORY ADDRESS switches to the decimal 8 position and again depress the SINGLE STEP CLOCK momentary switch. Now, set the MEMORY ADDRESS switches to the decimal 9 position and again depress the SINGLE STEP CLOCK momentary switch. Thus far in the procedure, we have executed microinstruction 8 which sets register 1 to the value five. If we leave the MEMORY ADDRESS switches in the decimal 9 position and begin depressing the SINGLE STEP CLOCK momentary switch, the contents of Register 0 will be increased by the value five. This will be equivalent to a sequence of 0, 5, 10, 15, 4, 9, 14, 3, 8, etc., in a

"magnitude only" number system. This output is viewed on the DATA DISPLAY LED's when the RAM & MUX SELECT switches are in the decimal 1 position. This microinstruction represents a register-to-register arithmetic addition within the Am2901 Microprocessor.

| BAM&<br>UUX       | 7                                     | 6                 | 5      | 4                  | 3                   | 2                 | 1             | 0           | NOTES                     |

|-------------------|---------------------------------------|-------------------|--------|--------------------|---------------------|-------------------|---------------|-------------|---------------------------|

| MEMORY<br>ADDRESS | BHANCH<br>ADDRESS<br>BH3 BH2 BH1 BH30 | P2 P1 P0          | SULLCT | SOURCE<br>SI   607 | C <sub>11</sub> ALU | ^.<br>^3 ^2 ^1 ^u | 83 82 B1 80   | 03 02 01 00 | AEXT OATA ABURESS CONTROL |

| 0                 |                                       |                   | 011    | 011                | 1000                |                   | 0000          |             | INC R.                    |

| 2                 |                                       |                   | 011    | 011                | 0000                | 0000              | 0000          | 0011        | DEC RO                    |

| 3                 | i                                     |                   |        |                    |                     |                   |               |             |                           |

| 5                 |                                       |                   |        | -                  | [                   |                   |               |             |                           |

| 6                 |                                       |                   |        |                    |                     |                   |               |             |                           |

| 7<br>8            |                                       |                   | 011    | 011                | 100                 |                   | 0000          |             | CLE Ro                    |

| 9                 |                                       |                   | 011    | 711                | 0000                | 0001              | 0000          | 0101        | R, = 5<br>R, ← R, + R,    |

| 10                |                                       |                   |        | J J J 1            |                     |                   |               |             |                           |

| 11                |                                       | — <del>-</del>  - |        | <del>-</del>       | -                   |                   |               |             |                           |

| 13                |                                       |                   |        | - <del>  -</del>   |                     |                   | - <del></del> |             |                           |

| 14                |                                       |                   |        |                    |                     |                   |               |             |                           |

| 15                |                                       |                   |        | i                  |                     |                   |               |             |                           |

BLANK - DON'T CARE

# Programming Exercise #4 - Continue and Branch Next Instructions in the Am2909 Microprogram Sequencer

The next few exercises will examine various functions for the control of the next microinstruction address. Field 6 of the microprogram memory word contains a number of functions that are executed by the next address control PROM associated with the Am2909 Microprogram Sequencer. These functions are shown on page 3-5 of the discussion on the operation of the Am2900 Kit. Exercises 1, 2, and 3 demonstrated a few of the functions of the Am2901 Microprocessor. All of these microinstructions were executed with the RUN/LOAD switch in the LOAD position. In order to execute the microinstructions associated with the next address control of the Am2909 Microprogram Sequencer, it will be necessary to switch the RUN/LOAD switch to the RUN position. However, in order to load the microprogram memory, the RUN/LOAD switch must be in the LOAD position.

First, the data on the programming table of the exercise 4 worksheet should be loaded into the microprogram memory. This exercise demonstrates the CONTINUE (or EXECUTE) operation as well as the BRANCH (or JUMP) operation in next microinstruction select control. After the microprogram memory has been loaded, the MEMORY ADDRESS switches should be placed in the decimal 0 position and the SINGLE STEP CLOCK momentary switch depressed one time. This will load the contents of memory address zero into the pipeline register. This is necessary to initialize the pipeline register so that the instruction sequence in the Exercise 4 worksheet can be executed. If this step is not performed, the current contents of the pipeline register are not known and the next microprogram memory address will most likely not be as determined from the worksheet. Now, the RUN/LOAD switch should be changed to the RUN position. If the RAM & MUX SELECT switches are placed in the decimal 0 position, the output of the Am2909 Microprogram Sequencer can be viewed on the DATA DISPLAY LED's. This display represents the address of the next microinstruction. At this point in the execution of the exercise, the DATA DISPLAY should show decimal nine (1001). As the SINGLE STEP CLOCK momentary switch is depressed, the sequence on the DATA DISPLAY should be 9, 6, 10, 11, 12, 13, 14, 15, 3, 0, 9, 6, etc. Microinstruction at address 0, 3, 6, 9, and 15 are BRANCH instructions while microinstructions at addresses 10, 11, 12, 13, and 14 are CONTINUE instructions.

The purpose of this exercise, of course, is to demonstrate the simple CONTINUE and BRANCH instructions used throughout microprogram memory next address control.

AND

BRANCH

### MICROPROGRAM MEMORY

| RAM &<br>MUX | ,                 |                                 | 5               | 4             | 3              | ?                                     | 1                                                           | 0           | пот                | ES      |

|--------------|-------------------|---------------------------------|-----------------|---------------|----------------|---------------------------------------|-------------------------------------------------------------|-------------|--------------------|---------|

|              | BRANCH<br>ADDRESS | MEXT<br>MINSTRUCTION<br>CONTROL | DEST.<br>SELECT | SOURCE        | ALU            | .v.                                   | .0.                                                         | .0.         | NEXT               | DATA    |

| ADDRESS      |                   | P3 P2 P1 P0                     | S 18 17 16      | SELECT SELECT | C <sub>n</sub> | A3 A2 A1 A0                           | B <sub>3</sub> B <sub>2</sub> A <sub>1</sub> N <sub>0</sub> | 03 02 01 00 | ADDRESS<br>CONTHOL | CONTROL |

| 0            | 1001              | 0001                            |                 |               |                | · · · · · · · · · · · · · · · · · · · |                                                             |             | BR 9               |         |

|              |                   |                                 |                 |               |                |                                       |                                                             |             |                    |         |

| 2            |                   |                                 |                 |               |                |                                       |                                                             |             |                    |         |

| 3            | 0000              | 0001                            |                 |               |                |                                       |                                                             |             | Beo                | -       |

| 4            |                   |                                 |                 |               |                |                                       |                                                             |             |                    |         |

| 5            |                   |                                 |                 |               |                |                                       |                                                             |             |                    |         |

| 6            | 1010              | 0001                            |                 |               |                |                                       |                                                             | ·           | BRIO               |         |

| 7            |                   |                                 |                 |               |                |                                       |                                                             |             |                    |         |

| B            |                   |                                 |                 |               |                |                                       |                                                             |             |                    |         |

| 9            | 0110              | 0001                            |                 |               | <u> </u>       |                                       |                                                             |             | BR6                |         |

| 10           |                   | 0010                            |                 |               |                |                                       |                                                             |             | CONT               |         |

| 11           |                   | 0010                            |                 |               |                |                                       |                                                             |             | CONT               |         |

| 12           |                   | 0010                            |                 |               |                |                                       |                                                             |             | CONT               | _       |

| 13           |                   | 0010                            |                 |               |                |                                       |                                                             |             | CONT               |         |

| 14           |                   | 0010                            |                 |               |                |                                       |                                                             |             | CONT               |         |

| 15           | 0011              | 0001                            |                 |               |                |                                       |                                                             |             | BR3                |         |

BLANK - DON'T CARE

# INSTRUCTION SEQUENCE; 0,9,6,10,11,12,13,14,153,0, ETC

## Programming Exercise #5 - Looping in Microprogram Memory

The purpose of this exercise is simply to demonstrate the technique of looping within the microprogram memory. This particular demonstration does not make provision for bracking out of the loop in any fashion. While this is not the normal case, it does provide the student with a view of what is involved in getting into and executing a loop. The loop is normally terminated by using one of two types of instructions. The first type of instruction would be test-end-of-loop and either repeat the loop if the condition is not true or continue out of the loop if the condition is true. When the "continue out of the loop" microinstruction is performed, a POP is executed to keep the stack maintained properly. The second technique for escaping a loop is to perform a conditional branch microinstruction somewhere within one of the loop microinstructions and when the test condition finally becomes true, a branch from the loop is made. Again, once out of the loop the first microinstruction should be a POP to perform the file maintenance.

Once the data on the worksheet associated with Exercise 5 has been loaded in the microprogram memory, the MEMORY ADDRESS select switches should be placed at decimal 0 and the SINGLE STEP CLOCK momentary switch depressed. Now, the RUN/LOAD select switch should be changed to the RUN position. If the RAM & MUX SELECT switches are placed in the decimal O position, the DATA DISPLAY LED's will view the Am2909 Microprogram Sequencer next address output. At this point, the DATA DISPLAY will show decimal 1. As the SINGLE STEP CLOCK momentary switch is depressed, the DATA DISPLAY LED's sequence will follow the pattern of 1, 2, 3, 4, 5, 6, 7, 8, 9, 10, 11, 12, 3, 4, 5, etc. Thus, the microinstruction 3 and proceeding through microinstruction 12, at which point a loop back to microinstruction 3 is performed. This loop is made possible by using the file reference next address microinstruction. A PUSH was performed at microword 2 so that the word currently on the stack is address 3. Thus, each time the file reference instruction is executed at microword 12, the next address from the Am2909 Microprogram Sequencer is microinstruction address 3.

| RAM &   |                                      | 6           | 5        |              |      | 4                | 1              |   | 3         |     |    | 2   |   | l    | 1       |    | 0              |   | NOI                        | ES              |

|---------|--------------------------------------|-------------|----------|--------------|------|------------------|----------------|---|-----------|-----|----|-----|---|------|---------|----|----------------|---|----------------------------|-----------------|

| AUDRESS | PRANCH<br>APPRESS<br>BR3 PR7 PH1 BR0 | P3 P2 P1 P0 | 3        | FST.<br>LECT | MUXO | SOURCE<br>SELECT | c <sub>n</sub> |   | ΛLU<br>14 | 13  | ۸3 | ·Λ· |   | В3 Е | B B1 P0 | 03 | D <sub>2</sub> |   | NEXT<br>ADDRESS<br>CONTROL | DATA<br>CONTROL |

| 0       | ·                                    | 0010        |          |              |      |                  |                |   |           |     |    |     |   |      |         |    |                |   | CONT                       |                 |

| 1       |                                      | 0010        |          |              |      |                  |                |   |           | _]  |    |     |   |      |         | Ī  | •••            |   | CONT                       |                 |

| ?       |                                      | 1001        |          |              |      |                  |                |   |           |     |    |     |   |      |         | ]_ |                |   | PUSH                       |                 |

| 3       |                                      | 0010        |          |              |      |                  |                | _ |           |     |    |     |   |      |         |    |                |   | CONT                       |                 |

| 4       |                                      | 0010        | <u> </u> |              | _].  |                  |                |   |           | ╛   |    |     |   |      |         |    |                |   | CONT                       | _               |

| 5       |                                      | 0010        |          | -            | _    |                  |                |   |           | _   |    |     |   |      |         |    |                |   | CONT                       |                 |

| б.      |                                      | 0010        |          |              | _    |                  |                |   |           | _[. |    |     |   |      |         | l_ |                |   | CONT                       |                 |

| 7       |                                      | 0010        |          | [            | _ .  |                  |                |   |           |     |    |     |   |      |         |    |                |   | COUT                       |                 |

| 8       |                                      | 0010        |          |              | _    |                  |                |   |           | _[  |    |     |   |      |         |    |                |   | CONT                       |                 |

| 9       |                                      | 0010        | _ _      |              | _    |                  | $\Box$         |   |           | _]. |    |     |   |      |         |    |                |   | CONT                       |                 |

| 10      |                                      | 0010        |          |              | _    |                  | _              |   |           | ╝.  |    |     |   |      |         |    |                |   | CONT                       |                 |

| 13      |                                      | 0010        | _        | [_           | _ .  |                  | _              |   |           | 1   |    |     |   |      |         |    |                |   | CONT                       |                 |

| 12      |                                      | 0111        |          |              |      | _                |                |   |           | ].  |    |     |   |      |         |    |                |   | FILE REF                   |                 |

| 13      |                                      |             |          |              | _    |                  | _              | _ |           | _[_ |    |     |   |      |         |    |                |   |                            |                 |

| 14      |                                      |             | -        |              | .    |                  | _              |   |           | - - |    | _   | [ |      |         |    |                | [ |                            | _               |

| 15      |                                      |             |          |              | Ì    | .                | - 1            |   |           | 1   |    |     |   |      | i       |    |                |   |                            |                 |

BLANK - DON'T CARE

# INSTRUCTION SEQUENCE: 0,1,2,3,4,5,6,7,8,9,10,11,12,3,4,67C

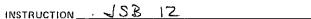

## Programming Exercise #6 - Executing a Subroutine in Microprogram Control

The purpose of this exercise is to demonstrate the technique of subroutining in microprogram memory. Microinstruction 3 executes a jump-to-subroutine at microinstruction 12. The subroutine at microinstruction 12 is three microinstructions in length covering the microprogram memory space between microinstruction 12 and microinstruction 14. The basic microinstruction sequence between microword 0 and microword 6 is simply a continue sequence between 0 and 3 as well as from 4 to 6. At microword 6, a branch to word 0 is performed.

This exercise is executed by first loading the microprogram memory with the data on the worksheet. Once the microprogram memory has been loaded, the MEMORY ADDRESS select switches should be placed in the decimal 0 position and the SINGLE STEP CLOCK momentary switch should be depressed. Now, the RUN/LOAD select switch should be placed to the RUN position and the RAM & MUX SELECT switches placed to the decimal 0 position. This alllows the DATA DISPLAY LED's to view the output of the Am2909 Microprogram Sequencer. The current display should be decimal value 1. As the SINGLE STEP CLOCK momentary switch is depressed, the DATA DISPLAY should execute the sequence 1, 2, 3, 12, 13, 14, 4, 5, 6, 0, 1, 2, 3, 12, etc.

| HAN S<br>MUX     | <i>i</i>        | 6                                      | 5                | 4             | 3                | 2           | 1            | 0                                                           | NO                         | TES             |

|------------------|-----------------|----------------------------------------|------------------|---------------|------------------|-------------|--------------|-------------------------------------------------------------|----------------------------|-----------------|

| VENORY<br>OURFSS | BB3 BB3 BB4 BB6 | athstruction<br>CONTROL<br>P3 P2 P1 P0 | <del>  _ '</del> | SOURCE SELECT | C <sub>n</sub>   | ^3 ^2 ^1 ^0 | n3 o5 '81 80 | D <sub>3</sub> D <sub>2</sub> D <sub>1</sub> D <sub>0</sub> | MEXT<br>ADDRESS<br>CONTROL | DATA<br>CONTROL |

| 1                |                 | 0010                                   |                  |               |                  |             |              |                                                             | CONT                       |                 |

| 3 4              | 1100            | 0101                                   |                  | -             | -  <br> -        |             |              |                                                             | JSB 12                     |                 |

| 5<br>6           |                 | 0010                                   |                  |               | <br> -           |             |              |                                                             | CONT                       |                 |

| 7 8              |                 |                                        | -                |               | - - <del>-</del> |             |              |                                                             | BIS D                      |                 |

| 9                |                 |                                        |                  |               |                  |             |              |                                                             |                            |                 |

| 11               |                 | 0010                                   |                  |               |                  |             |              |                                                             | CONT                       |                 |

| 13               |                 | 00 10                                  |                  |               |                  |             |              | <u> </u>                                                    | CONT<br>RTS                |                 |

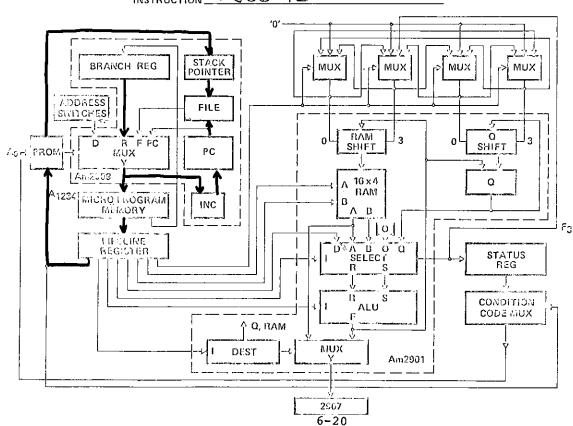

# Programming Exercise #7 - Nesting Subroutines

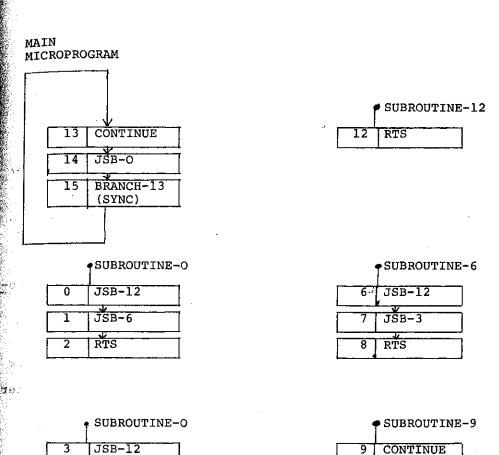

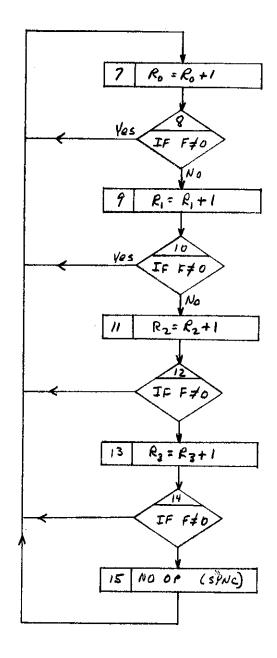

This exercise demonstrates the technique of nesting subroutines in microprogram memory. The subroutines are nested four levels deep in this example. The main microprogram resides at microinstructions 13, 14, and 15. The microinstruction at word 14 is a jump-to-subroutine at address 0. This is shown on the flow diagram below. Once at subroutine 0, we see the first instruction is a jump-to-subroutine at microinstruction 12. The subroutine at microinstruction 12 is a single microinstruction subroutine resulting in a return-from-subroutine. The microinstruction at address 1 is another jump-to-subroutine at microprogram address 6. The subroutine beginning at microprogram address 6 again executes a jump-to-subroutine at address 12. Again, the single microinstruction subroutine is executed and the microprogram control returns to address 7 where another jump-tosubroutine is found. Here, the jump-to-subroutine takes the next microinstruction from word 3. The microinstruction at word 3 again executes a jump-to-subroutine at word 12. The single microinstruction subroutine at location 12 is now executed and the microprogram control returns to address 4. The microprogram instruction at word 4 is another jump-to-subroutine at microprogram memory word 9. Microprogram memory word 9 is a continue instruction and microprogram memory word 10 is a return-from-subroutine instruction. The flow is such that subroutine 9 returns to subroutine 3 which returns to subroutine 6 which returns to subroutine 0 which returns to the main program.

From this example, several observations can be made about subroutining in microprogram control. First, we have nested subroutines up to four levels deep using the Am2909 stack. Second, the stack has maintained the correct return linkage throughout the various subroutine calls and returns. Third, the subroutine at microinstruction 12 has been used at more than one level of subroutining.

The purpose of this exercise has been to demonstrate nesting of four levels of subroutining. Note that each level of subroutining required one return address location in the PUSH/POP stack. Recalling the discussion on looping in Exercise 5, a PUSH onto the stack was performed to supply the reference address for the loop. Thus, it should be understood that up to four levels of loops and subroutines can be intermixed in any fashion. One word of the stack is used for each reference address required. For example, a subroutine might contain a loop which contains another subroutine which contains another loop. This would utilize the four levels of stack depth within the Am2909 Microprogram Sequencer.

NAME: NESTING

SUBROUTINES

### MICROPROGRAM MEMORY

| B MAN.            | , ,                                   | 6           | 5               | Т  | 4                | Γ   | 3   | 2   | 1                                                           | 0           | мо.                        | ES   |

|-------------------|---------------------------------------|-------------|-----------------|----|------------------|-----|-----|-----|-------------------------------------------------------------|-------------|----------------------------|------|

| MEMORY<br>ADDRESS | 884NCH<br>ADDRESS<br>883 882 881 8130 | P3 F2 P1 F0 | DEST.<br>SELECT | 16 | SOURCE<br>SELECT | C,1 | ALU | ·A' | B <sub>3</sub> B <sub>2</sub> B <sub>1</sub> B <sub>0</sub> | 03 02 01 00 | NEXT<br>ADDRESS<br>CONTROL | DATA |

| 0                 | 1100                                  | <del></del> |                 | ┪  | <b></b>          | -   |     |     |                                                             | . <u> </u>  | 188 12                     |      |

| 1                 | 0110                                  | 0111        |                 |    |                  |     |     |     |                                                             |             | 15B6                       |      |

| 2                 |                                       | 0101        |                 |    |                  |     | •   |     |                                                             |             | RTS                        |      |

| 3                 | 1100                                  | 0111        |                 |    |                  |     |     |     |                                                             |             | 15812                      |      |

| 4                 | 1001                                  | 0111        |                 |    |                  |     |     |     |                                                             |             | JSB9                       |      |

| 5                 |                                       | 0101        |                 |    |                  |     |     |     |                                                             |             | RTS                        |      |

| 6                 | 1100                                  | 0111        |                 |    |                  |     |     |     |                                                             |             | JS8 12                     |      |

| 7                 | 0011                                  | 0111        |                 |    |                  |     |     |     |                                                             |             | J\$83                      |      |

| 8                 |                                       | 0101        |                 |    |                  |     |     |     |                                                             |             | RTS                        |      |

| 9                 |                                       | 0001        |                 |    |                  |     |     |     |                                                             |             | CONT                       |      |

| 10                |                                       | 0101        | i               |    |                  |     |     |     |                                                             |             | RTS                        |      |

| 11                |                                       |             |                 |    |                  |     |     |     |                                                             |             |                            |      |

| 12                |                                       | 0101        |                 |    |                  |     |     |     |                                                             |             | RTS                        |      |

| 13                |                                       | 0010        |                 |    |                  |     |     |     |                                                             |             | CONT                       |      |

| 14                | 0000                                  | 0111        |                 |    |                  |     |     |     |                                                             |             | JS8 0                      |      |

| 15                | 1101                                  | 0000        | 1               | _L |                  |     |     |     |                                                             |             | 3R 13                      |      |

BLANK - DON'T CARE

Actual Address flow is:

JŠB-9

RTS

13, 14, 0, 12, 1, 6, 12, 7, 3, 12, 9, 10, 5, 8, 2, 15, 13, etc.

10 | RTS

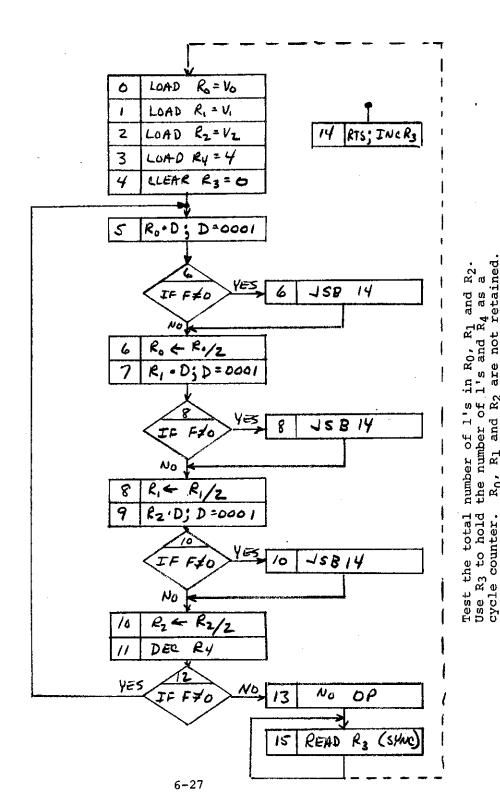

### Programming Exercise #8 - Combining the Am2901 and Am2909 to Perform Conditional Branching

This is the first exercise that combines both the Am2901 and Am2909 functions. It is used to demonstrate the technique of conditional branching in microprogram control. The microinstruction at word 1 contains a test on the carry flag whereby a conditional branch occurs if the carry output is logic 1.

This exercise should be executed in the following manner. After the data on the worksheet has been loaded into the microprogram memory, the MEMORY ADDRESS select switches should be placed at decimal 0 and the SINGLE STEP CLOCK momentary switch depressed. Now, the RUN/LOAD select switch should be placed in the RUN position. If the RAM & MUX select switches are placed in the decimal 0 position, the Am2909 Microprogram Sequencer next microinstruction address output is viewed. The DATA DISPLAY LED's will currently contain decimal value 1. As the SINGLE STEP CLOCK momentary switch is depressed, the data display pattern will follow a 1, 2, 0, 1, 2, 0 pattern until the carry output is a "logic 1". At this point, the next address will branch from microprogram memory word 1 to microprogram memory word 15 and then to microprogram memory word 0. This 1, 2, 0 loop will be repeated 15 times until the next carry flag occurs on the 16th interation and a branch to microword 15 again occurs.

The way this exercise operates is to take the contents of register 0 and increment the current value on microword 0. The instruction at microword 1 is used to test the carry flag stored in the status register. If the carry flag is logic 1, a branch to microword 15 is performed. At microword 15, a continue instruction is executed which results in an end around microword 0.

While this exercise is contained in the static testing mode description, it can also be used in the dynamic testing mode. Microinstruction 15 will occur once every 48 clock cycles. Because the design of the Am2900 Kit uses the Am2909 Sequencer with the carry input tied HIGH, each time address 15 occurs at the Am2909 outputs, the Am2909 carry output will be HIGH. It is this Am2909 carry output that is connected directly to the SYNC TEST turret terminal on the kit printed circuit board. Thus, in this example, the SYNC TEST turret terminal provides a convenient point to synchronize the oscilloscope to see the entire 48 word microprogram sequence. Likewise, the ADDRESS SYNC turret terminal can be used to view particular microinstruction address execution on an oscilloscope. That is, by setting the MEMORY ADDRESS select switches to a particular decimal value, a HIGH output on the ADDRESS SYNC turret terminal results each time the Am2909 Microprogram Sequencer address matches that of the MEMORY ADDRESS select switches. This allows one trace of a multiple trace oscilloscope to be connected to the ADDRESS SYNC turret terminal and the execution of a particular address studied. This will be discussed in more detail in the dynamic operational description of the programming exercises.

#### MICROPROGRAM MEMORY

| HAM &      | ,                                    | 6                | 5                  | 4                                | 3               | 2                                         | 1             | 0           | uq                         | TES             |

|------------|--------------------------------------|------------------|--------------------|----------------------------------|-----------------|-------------------------------------------|---------------|-------------|----------------------------|-----------------|

| MINOR      | FRANCH<br>ADDRESS<br>BR3 BR24BH1 HHm | #1851 PT ( 100 N |                    | SOURCE<br>SELECT<br>No. 12 11 10 | C <sub>11</sub> | ,,,<br>,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, | 'в'<br>Вз     | 03 07 01 00 | NEXT<br>ADDRESS<br>CONTROL | DATA<br>CONTROL |

| ADDRIESS   |                                      | 0010             | 011                | . 011                            | 1000            |                                           | 0000          |             |                            | INC 60          |

| <u>-</u> - |                                      |                  | 001                | <u> </u>                         |                 |                                           | <del></del>   |             |                            | Beis Cnry       |

| 3          | 0000                                 | 0001             | 001                |                                  |                 |                                           |               |             | BR O                       | No or           |

| 4          |                                      |                  | -   <del>-</del> - |                                  |                 |                                           |               |             |                            |                 |

| 5          |                                      |                  | - <del> </del>     |                                  |                 | ×                                         |               |             | _                          |                 |

| 7          |                                      |                  |                    | -                                |                 |                                           |               |             |                            |                 |

| . 3        |                                      |                  |                    | <u> </u>                         |                 |                                           | <del></del> - |             |                            | -               |

| 9          |                                      |                  | -                  |                                  | _               |                                           |               |             |                            |                 |

| 10         |                                      | <del>-</del>     |                    | _                                |                 |                                           |               |             |                            |                 |

| 12         |                                      |                  |                    |                                  |                 |                                           |               |             |                            |                 |

| 13         |                                      |                  |                    |                                  |                 |                                           |               |             |                            |                 |

| 14         |                                      | 0010             | 001                |                                  |                 |                                           |               |             | CONT                       | No OP           |

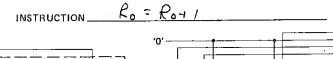

INSTRUCTION

EXERCISE NUMBER:

# NAME: EXAMPLE OF "B" ACCESS TIME

# Programming Exercise #9 - Measuring the B Address Access Time

The purpose of this exercise is to demonstrate the technique used to measure the access time of the Am2901 RAM with respect to the B address. First, microprogram memory word 0, 1, 14, and 15 should be loaded as shown on the worksheet. Now, the CLOCK SELECT switch should be in the SINGLE STEP position and the RUN/LOAD select switch should be in the LOAD position. The MEMORY ADDRESS select switches should be in the decimal 0 position and the SINGLE STEP CLOCK momentary switch depressed. This initializes the pipeline register to a starting address. Next, change the RUN/LOAD select switch to the RUN position. Now, depress the SINGLE STEP CLOCK momentary switch two times so as to execute the microinstructions at word 0 and word 1. This performs the loading of register 0 with all zeros and register 15 with all ones.

Now, if a pulse generator has been connected to the PULSE GENERA-TOR inputs, when the CLOCK SELECT switch is changed to the PULSE GEN-ERATOR position, the Am2900 Evaluation Kit will be operating in the dynamic mode. The SYNC TEST turret terminal can be used as a convenient oscilloscope sync point. The microprogram control will now be executing the microinstructions at word 14 and word 15.

The two microinstructions at word 14 and word 15 cause the B address to be changed from all zeros to all ones and then back to all zeros. The Am2901 RAM data output for these two registers is also all zeros and all ones. Thus, if the Am2901 Y outputs are probed with an oscilloscope and the Am2901 B inputs are also examined with an oscilloscope, the differential time between the B address change and the Y data output is measured - the B access time. The path selected in this example is to use the ALU "OR" function with the B and O source operands. In this example, the RAM is being re-written on each microinstruction; however, the no operation destination control instruction can also be used.

From this example, the user should recognize that the B address fields and the data fields could be selected in any fashion so that various patterns can be examined. Likewise, the entire Am2901 RAM might be initialized to all ones, all zeros, or a checkerboard pattern if the user desires. It should also be recognized that similar techniques can be used to measure various propagation delays such as the D inputs to the Y outputs, the A address inputs to the Y address outputs, carry-in to carry-out and so forth. In fact, almost all of the combinatorial propagation delays shown in Table II of the Am2901 data sheet can be measured in this manner. The key item to be remembered in performing any of these measurements is that only the variable to be measured changes between microcycles. That is, all other inputs to the Am2901 should be held constant except for the path being measured. For example, when measuring the carry input to carry output propagation delay, only the carry input should be changed during the microinstruction time of interest.

#### MICROPROGRAM MEMORY

|     | HAM &             | 1   |                 |     | ,           |       |                 |    |    | G  |    |    | T   |     | 5   |       | _  | Τ    |    | 1          |            |    | T   |     | ;  | 3   | -  | Γ        |   | 2   | _   |     |    |     | 1  |   |     |     | 0  |     | • | Γ |     |     | NO | TES |              |                 | _ |

|-----|-------------------|-----|-----------------|-----|-------------|-------|-----------------|----|----|----|----|----|-----|-----|-----|-------|----|------|----|------------|------------|----|-----|-----|----|-----|----|----------|---|-----|-----|-----|----|-----|----|---|-----|-----|----|-----|---|---|-----|-----|----|-----|--------------|-----------------|---|

|     |                   | ]   |                 |     | INRI<br>- 1 | E 5.5 |                 |    | 50 | ч. | нΩ |    | վ չ | į   | Sf. | L S T | T  | MIXX | ,  | 5/)<br>\$E | URC<br>LEC | E. |     |     |    | ALU | ,  |          |   | Α,  |     | -   |    |     | В' |   | 1   |     | D. |     |   |   |     | EXT |    |     | DAT          |                 | Ī |

|     | MEMORY<br>ADDRESS | s l | 3R <sub>3</sub> | 98  | 2 B         | R     | IR <sub>U</sub> | P3 | P  | 2  | Pı | Po | 1   | ŀ   | 8   | 17    | 16 | ž    | 1  | 2          | 1,         | ю  | - C |     | 15 | 14  | 13 | Ą        | ^ | 2 4 | 1 ^ |     | В3 |     |    | B | - 1 | 3 [ |    | - 1 |   |   | con | TRO | L  | -   | CONT         |                 |   |

|     | 0                 | - - |                 |     | _           |       | _               | 0  | (  | 2  | L  | 0  | 1   |     | 2   | l     | 1  |      | 1  |            | l          | L  | L   | _[. | 0  | Ī   | 1  |          |   |     |     |     | 0  | 0   | 0  | C |     | 0   | 0  | 0   | Ō | 0 | 20  | N   | Т  | 2   | s =<br>5 =   | 0               |   |

|     | 1                 |     | l               | 1   |             | L     | )               | C  | (  | )  | 0  | 1  | ļ_  | .11 | )   | L     | 1  | L    | 1  | _          | L          | 1  | ļ_  | _   | 0  | L   | 1  | _        |   |     |     | _ . | L  | L   | 1  | _ | L   |     | L  | Ĺ   | Ī | R | R   | 14  | /  | e,  | 5=           | ڪا:             | 1 |

|     | 2                 | 1   |                 |     |             |       |                 | _  |    |    |    |    | ļ_  | Ļ   |     |       |    | ļ_   | ļ_ |            |            |    | 1_  |     |    |     |    | _        |   |     |     |     |    |     |    |   | _   |     |    |     | _ |   |     |     |    |     |              |                 |   |

|     |                   |     | _               |     |             |       | _               | _  |    |    |    |    | -   | 1   |     |       |    | L    | _  |            |            |    | L   | 1   |    |     |    | <u> </u> |   |     |     |     |    |     |    |   | 1_  |     |    |     |   |   |     |     |    |     |              |                 |   |

|     | 4                 | 1   |                 |     |             |       | _               |    |    |    |    | _  | ļ_  |     |     | _:    |    |      | _  |            |            |    | L   | _   |    |     |    | L        |   |     |     |     |    |     |    |   | _[_ |     |    |     |   |   |     |     |    |     |              |                 |   |

|     | 5                 | 1   | _               |     |             |       |                 | _  |    | _  |    |    |     | L   |     |       |    | _    | _  |            |            | _  | L   |     |    |     |    | Ŀ        |   |     |     | L   |    |     |    |   |     |     |    |     |   |   |     |     |    |     |              |                 | _ |

|     | 6                 | L   | _               |     |             |       | _               |    |    |    |    |    |     |     |     |       |    | L    |    |            |            |    |     | ì   |    |     |    |          |   |     |     | -   |    |     |    |   |     |     |    |     |   |   |     |     | _  |     |              |                 |   |

| 1   | 7                 | L   |                 |     |             |       |                 |    |    | _  |    |    |     |     |     |       |    |      |    |            |            |    |     |     |    |     |    |          |   |     |     | T   |    |     |    |   |     |     |    |     |   |   |     |     |    |     |              |                 |   |

|     | 8                 |     |                 |     |             |       |                 |    |    |    |    |    |     |     |     |       |    | Ī    |    |            |            |    | Ī   |     |    |     |    |          |   |     |     | 7   |    |     |    |   | Ī   |     |    |     |   |   |     |     |    |     |              | _               | _ |

| ĺ   | 9                 | I   |                 |     |             | _     | ĺ               |    |    |    |    |    |     | ï   |     |       | _  | Γ    | Ī  |            |            |    |     | T   |    |     | _  |          |   |     |     | 1   |    |     |    |   | T   |     | _  |     |   | _ |     |     |    |     |              |                 | ٦ |

|     | . 10              |     |                 |     |             |       |                 |    |    |    |    |    |     | Г   | _   |       |    |      |    |            |            |    |     |     |    | -   |    | _        |   |     |     | 1   |    |     |    |   | ╎   |     |    |     |   |   | _   |     |    |     |              |                 | ٦ |

|     | 11                |     |                 |     |             |       |                 |    |    |    |    |    |     | İ   |     |       |    |      | -  |            |            |    |     |     |    |     |    |          |   |     |     | T   |    |     |    | · |     |     |    |     | 1 |   |     |     |    |     |              |                 | 1 |

|     | 12                | Ţ   |                 |     |             |       |                 |    |    |    |    |    |     | Ī   |     |       |    |      | ï  |            |            | _  |     | -/- |    |     |    | _        |   |     |     | 7   |    |     |    |   | -1- |     |    |     |   |   |     |     |    |     |              | •               | ٦ |

| • [ | 13                | Γ   | _               |     |             |       | T               |    |    |    |    |    |     | Ī   | _   |       |    |      |    | _          |            |    | !-  | 1   |    |     |    |          |   |     |     | T   |    | _   |    |   | Τ   |     |    |     | _ |   | _   |     |    |     |              |                 | 7 |

| Ì   | 14                |     |                 | _   | _           |       |                 | 0  | C  | )  | L  | )  |     | (   | כ   |       | 1  | _    | 6  | )          | ı          | 1  |     | (   | 2  | ī   | ı  |          |   |     |     | 1   | )( | ) ( | 0  | 0 |     |     |    |     | 7 | ٥ | 01  | דנ  | -  | RE  | 40 /         | e.              | 1 |

| [   | 15                | l   |                 |     | 1           | 0     | <u> </u>        | 0  | (  | 2  | 2  | Ĺ  |     | (   |     | Ĺ     |    |      | C  |            |            | Ī  |     | -1  | 0  | ī   | ĺ  |          |   |     |     | T   | ī  | Ì   | Ī  | Ī | T   |     |    | _   |   |   |     | 71  | 4  | REI | 10 /<br>10 ( | R <sub>15</sub> | ٦ |