Bit-Slice Design: Controllers and ALUs

by Donnamaie E. White

Copyright © 1996, 2001, 2002 Donnamaie E. White

- Pre-Introduction

- Selection of the Implementation

- Microprogramming

- Advantages of LSI

- The 2900 Family

- Language Interrelationships

- Controller Design

- Constructing the CCU

- Sequential Execution

- Multiple Sequences

- Start Addresses

- Mapping PROM

- Unconditional Branch

- Conditional Branch

- Timing Considerations

- Pipelining

- Improved Architecture

3. Adding Programming

Support to the Controller

- Expanded Testing

- Subroutines

- Nested Subroutines

- Stack Size

- Loops

- Am29811

- Am2909/11

- CASE Statement (Am29803A)

- Microprogram Memory

- Status Polling

- Interrupt Servicing

- Implementation - Interrupt Request Signals

- Vector Mapping PROM

- Next Address Control

- Am2910

- Am2910 Instructions

- Control Lines

- Interrupt Handling

- Am2914

- Interconnection of the Am2914

6. The ALU and Basic Arithmetic

- Further Enhancements

- Instruction Fields

- Instruction Set Extensions

- Sample Operations

- Arithmetic -- General

- Multiplication with the Am2901

- Am2903 Multiply

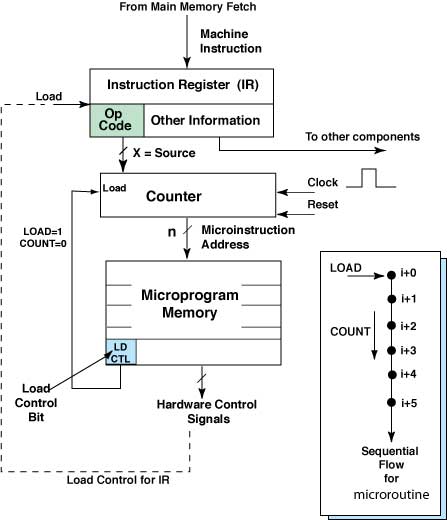

Simple ControllerLast Edit October 10, 1996; July 9, 2001 Start AddressIf the controller is a CCU, the start address of each microroutine is derived from the current machine instruction. At the minimum, an instruction register must be added between the data bus and the counter data inputs to store this instruction. A load control bit must be added to the microword for the instruction register, which must load prior to the counter load (see Figure 2-5). This scheme requires that the op code equal the high-order bits of the start address, with the low-order bits tied to logical "0". This is necessary to allow the starting addresses to be separated by the mini mum number of addresses required by the longest microroutine. Figure 2-5 Basic CCU (x, number of bit in op code; n, number of bits in counter address)

Assume that no machine instruction is anticipated to take more than 16 microinstructions to execute. Also, assume a 12-bit address and a 4K PROM memory. The op code must then be no more than 8 bits in length, and the lower 4 bits of the counter data inputs must be tied low (or to logical zero). Sixteen steps are are allowed per microroutine, and up to 256 different start addresses are possible with this configuration. The clock pulse required by the controller has not changed. Remember also that the width of the memory is not a function of its depth. This scheme is adequate if:

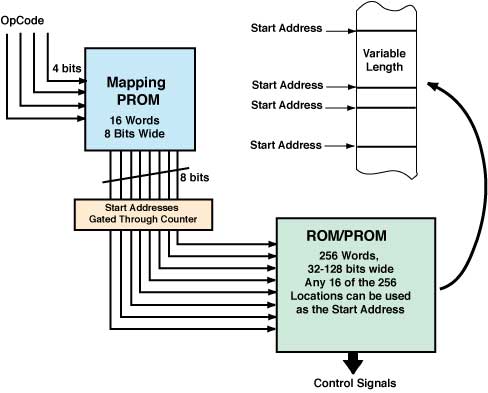

Mapping PROMIf fragmented space and reduced numbers of available op codes are not acceptable, one solution is to add a mapping PROM between the instruction register and the counter. The op code is the address into the map, which in turn outputs the full start address of the microroutine to the counter, as shown in Figure 2-6. Start addresses may now be assigned at any location in the PROM memory rather than requiring them to be equidistant from each other, and microroutines may be compacted in this way to delete excessive fragmented space. (It is, however, a good idea to allow some unused areas within the PROM to allow for enhancement changes to the system.) The final placement of the microroutines in the production PROMs should be done after the debug cycle to minimize mapping PROM changes. This is where a development system is used to advantage. Figure 2-6 Mapping PROM

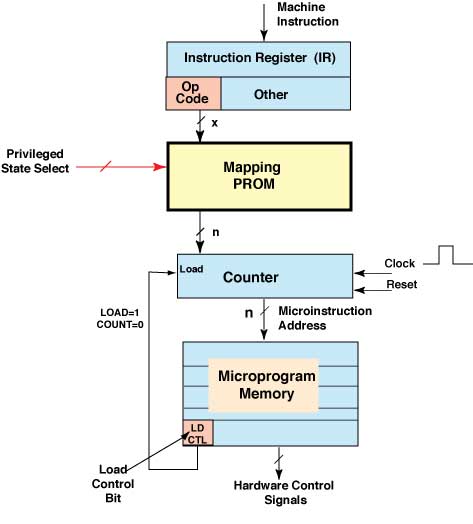

Another feature may be added once a mapping PROM approach is chosen. The mapping PROM may be made larger than required for normal running and contain address lines driven by switches to allow a Privileged State, where all op codes are valid, and a Normal State, where certain op codes are invalid, "trapping out" to an error trap address in the control memory. The control memory would not necessarily be larger than before. The CCU is shown in Figure 2-7. A fairly reasonable control system has been constructed which is acceptable is all of the microroutines are simple sequences. Figure 2-7 CCU with Mapping PROM

|