Bit-Slice Design: Controllers and ALUs

by Donnamaie E. White

Copyright © 1996, 2001, 2002, 2008 Donnamaie E. White

- Pre-Introduction

- Selection of the Implementation

- Microprogramming

- Advantages of LSI

- The 2900 Family

- Language Interrelationships

- Controller Design

- Constructing the CCU

- Sequential Execution

- Multiple Sequences

- Start Addresses

- Mapping PROM

- Unconditional Branch

- Conditional Branch

- Timing Considerations

- Pipelining

- Improved Architecture

3. Adding Programming Support to the Controller

- Expanded Testing

- Subroutines

- Nested Subroutines

- Stack Size

- Loops

- Am29811

- Am2909/11

- CASE Statement (Am29803A)

- Microprogram Memory

- Status Polling

- Interrupt Servicing

- Implementation - Interrupt Request Signals

- Vector Mapping PROM

- Next Address Control

- Am2910

- Am2910 Instructions

- JZ, CONT, JMAP

- CJP, CJV, LDCT, JRP, CJS

- JSRP, CRTN, RPCT, PUSH

- LOOP, CJPP, TWB

- Control Lines

- Interrupt Handling

- Am2914

- Interconnection of the Am2914

6. The ALU and Basic Arithmetic

- Further Enhancements

- Instruction Fields

- Instruction Set Extensions

- Sample Operations

- Arithmetic -- General

- Multiplication with the Am2901

- Am2903 Multiply

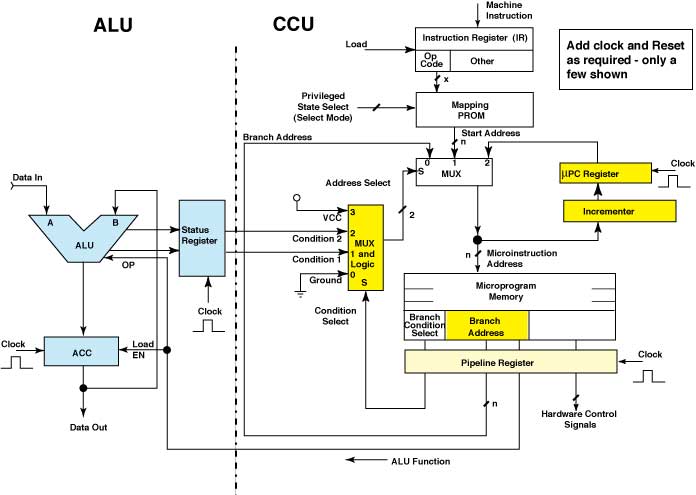

Simple Controller continuedLast Edit April 3, 1997; May 1, 1999; July 9, 2001 Improved ArchitectureThe CCU is improved by placing the next-address MUX to input directly into the PROM to avoid the counter set-up time. The counter then becomes one of three inputs into the next-address MUX. The condition select MUX must be replaced by equivalent logic to generate the two MUX select signals of the new start address MUX. The counter has moved to a position where it cannot receive a proper input. It must be replaced with a register, called the microprogram counter (µPC). The incrementer is connected to the PROM memory input and outputs to the µPC. The incrementer always contains the address being fetched plus 1. The outputs of the incrementer are gated into the µPC on the rising edge of the clock. The resulting configuration is shown in Figure 2-22. Figure 2-22 Completed Elementary System

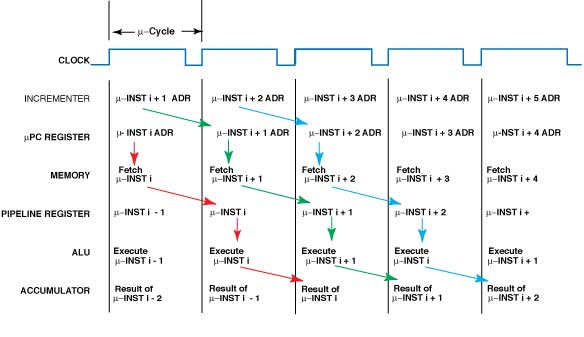

No Branch The timing diagram for Figure 2-22 for no-branch execution is shown in Figure 2-23. What exists now is a three-level pipeline. During the first microcycle, the memory is fetching microinstruction i. The address of microinstruction i is in the µPC. The incrementer is one instruction ahead, with the address of microinstruction i + 1. The pipeline register contains microinstruction i - 1, which is in execution. The ACC contains the results of microinstruction i - 2. The execution proceeds as in earlier diagrams. Figure 2-23 Microcycle Timing for the System in Figure 2-22, no branch

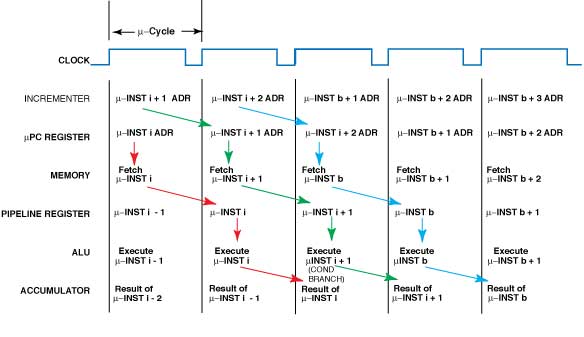

Improved Branching The difference between the design is shown in the activity which occurs when a branch is executed, as shown in Figure 2-24. Figure 2-24 Microcycle Timing for the System in Figure 2-22, Branch on Result of Microinstruction I (µ-INST. i)

On the second clock, the memory is fetching microinstruction i + 1, and the address of microinstruction i + 1 is in the µPC. The address of microinstruction i + 2 is in the incrementer. Microinstruction i is in the pipeline register and is being executed by the ALU. The result of microinstruction i - 1 is in the ACC. On the next clock, microinstruction i + 1 is loaded into the pipeline register. This is the conditional branch. The pipeline outputs the controls to the condition select logic which switches the MUX to pass the branch address. At the instant that the clock edge comes up, the µPC is loaded with the address of microinstruction i + 2. As soon as the outputs are available, if the MUX has not yet switched, address i + 2 will be sent to memory. The read access time of the PROM is greater than the propagation delay of the path through the pipeline, condition MUX, and next-address MUX, and is greater than the µPC register setup time and the propagation delay of its output through the next-address MUX. Any fluttering of the address inputs occurring from the start of a fetch of the branch address is irrelevant, since the memory output is not sensed until the next clock. Therefore, during the third cycle, the branch address is fetched. The incrementer now contains the address following the branch address. On the next clock, execution proceeds with no flushing of the pipe and with no extraordinary idle times. This is the desired CCU design. The cycle time is now (use Netscape!!!): [all times are maximum worst-case] CP = tpipeline clock to output + tpropagate cond. logic + tpropagate next-address MUX + tPROM read access + tregister setup (pipeline) Or, CP = tsetup µPC + t propagate next-address MUX + tPROM read access + t register setup (pipeline) Or, CP = tpipeline clock to output + tALU execution + tresister setup (ACC, Status) whichever is longer (whichever is the critical path). |