Bit-Slice Design: Controllers and ALUs

by Donnamaie E. White

Copyright © 1996, 2001, 2002, 2008 Donnamaie E. White

- Pre-Introduction

- Selection of the Implementation

- Microprogramming

- Advantages of LSI

- The 2900 Family

- Language Interrelationships

- Controller Design

- Constructing the CCU

- Sequential Execution

- Multiple Sequences

- Start Addresses

- Mapping PROM

- Unconditional Branch

- Conditional Branch

- Timing Considerations

- Pipelining

- Improved Architecture

3. Adding Programming Support to the Controller

- Expanded Testing

- Subroutines

- Nested Subroutines

- Stack Size

- Loops

- Am29811

- Am2909/11

- CASE Statement (Am29803A)

- Microprogram Memory

- Status Polling

- Interrupt Servicing

- Implementation - Interrupt Request Signals

- Vector Mapping PROM

- Next Address Control

- Am2910

- Am2910 Instructions

- JZ, CONT, JMAP

- CJP, CJV, LDCT, JRP, CJS

- JSRP, CRTN, RPCT, PUSH

- LOOP, CJPP, TWB

- Control Lines

- Interrupt Handling

- Am2914

- Interconnection of the Am2914

6. The ALU and Basic Arithmetic

- Further Enhancements

- Instruction Fields

- Instruction Set Extensions

- Sample Operations

- Arithmetic -- General

- Multiplication with the Am2901

- Am2903 Multiply

Refining the CCULast Edit November 2, 1996; May 1, 1999; July 7, 2001 Am2910 Instructions

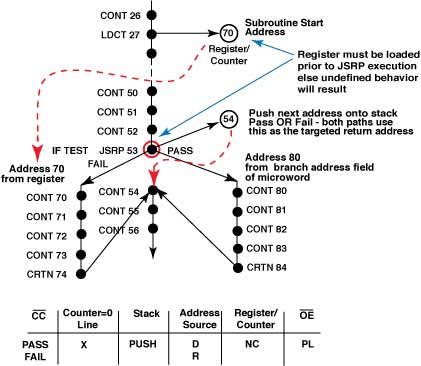

Figure 4-17 Conditional jump subroutine register/pipeline

(JSRP, 5, 0101).

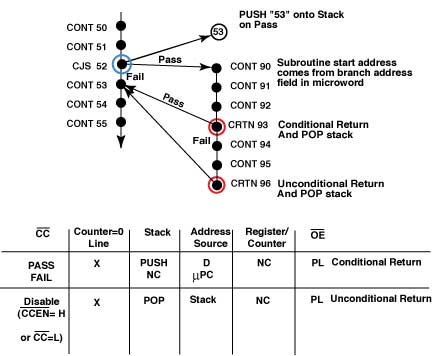

Figure 4-18 Conditional Return (CRTN, A, 1010)

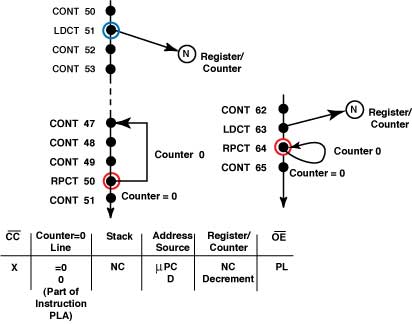

Figure 4-19 Repeat pipeline if counter not = 0 (RPCT, 9, 1001). (Loop on one or more statements, beginning address of loop in register (at the time of the RPCT statement).

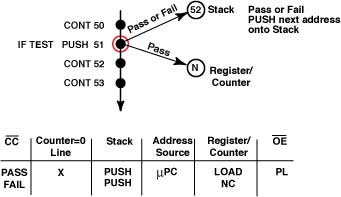

Figure 4-20 Push stack and condition load counter (PUSH, 4, 1000). This instruction must immediately precede the first statement in a loop controlled by LOOP or RFCT. |