Bit-Slice Design: Controllers and ALUs

by Donnamaie E. White

Copyright © 1996, 2001, 2002, 2008 Donnamaie E. White

- Pre-Introduction

- Selection of the Implementation

- Microprogramming

- Advantages of LSI

- The 2900 Family

- Language Interrelationships

- Controller Design

- Constructing the CCU

- Sequential Execution

- Multiple Sequences

- Start Addresses

- Mapping PROM

- Unconditional Branch

- Conditional Branch

- Timing Considerations

- Pipelining

- Improved Architecture

3. Adding Programming Support to the Controller

- Expanded Testing

- Subroutines

- Nested Subroutines

- Stack Size

- Loops

- Am29811

- Am2909/11

- CASE Statement (Am29803A)

- Microprogram Memory

- Status Polling

- Interrupt Servicing

- Implementation - Interrupt Request Signals

- Vector Mapping PROM

- Next Address Control

- Am2910

- Am2910 Instructions

- JZ, CONT, JMAP

- CJP, CJV, LDCT, JRP, CJS

- JSRP, CRTN, RPCT, PUSH

- LOOP, CJPP, TWB

- Control Lines

- Interrupt Handling

- Am2914

- Interconnection of the Am2914

6. The ALU and Basic Arithmetic

- Further Enhancements

- Instruction Fields

- Instruction Set Extensions

- Sample Operations

- Arithmetic -- General

- Multiplication with the Am2901

- Am2903 Multiply

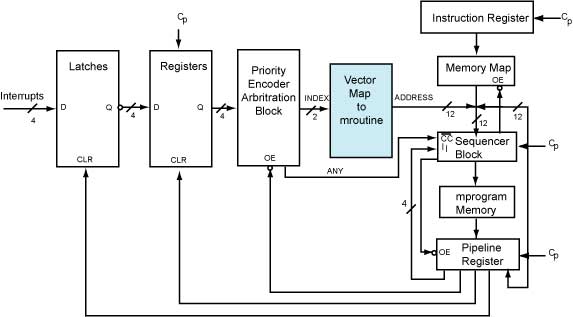

Refining the CCULast Edit November 2, 1996; May 1, 1999 Interrupt Servicing - ContinuedVector Mapping PROMRather than using the main microprogram memory to store a branch table, which requires a full microword to store what is essentially a branch address, it is better to use a vector mapping PROM. A vector mapping PROM is similar to the mapping PROM that was used earlier for the start address of the normal microroutines, with the vector mapping PROM providing the start addresses of interrupt service microroutines. The index bits from the priority encoder are the address bits supplied to the vector mapping PROM, and the PROM output is a full n-bit address. By using a PROM with tri-state output as the vector map, the map can share the microprogram address input with the mapping PROM and the branch address. The next-address control block must supply an OE'vector control line in this case. (See Figure 4-6.) Figure 4-6 Using a vector map

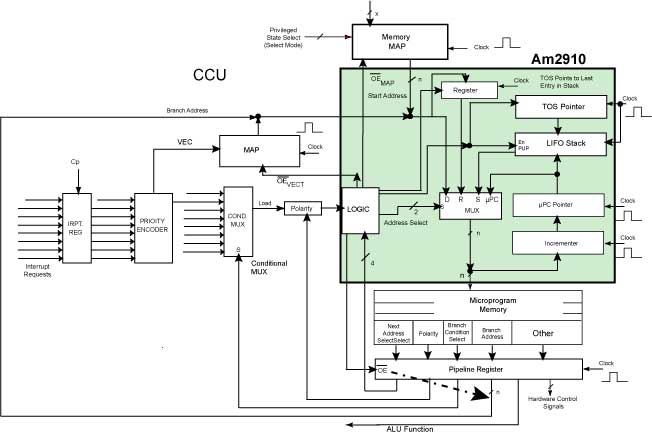

Next Address ControlThe next address control can be handled by an Am29811A and an Am25 LS139 decoder. The Am29811 supplies the output enables for the map and pipeline register. By decoding these two signals, the three output enables (map, pipeline, vector) are generated. The Am29811 has an instruction called CJV (Conditional Jump Vector), which operates as any other conditional instruction except that if COND = TRUE, the vector map is enabled and OE'map and OE'pipeline are used to disable the mapping PROM and the pipeline register. If the microprogram sequencer which was developed in Chapter 3 is modified by making the address register and the counter into one unit with the associated next-address control changes, then the register-counter, the next-address logic, the next-address MUX, the stack, the TOS pointer, the µPC register, and the incrementer exist as a single IC device. This is the Am2910 microprogram sequencer (dubbed "supersequencer"), which can address up to 4K of PROM memory. It is approximately equivalent to three Am2911s, and Am29811, and an Am25LS139. It is referred to as the "supersequencer" because it is powerful enough for most controller applications (see Figure 4-7). Figure 4-7 The AMD Am2910 Supersequencer - now obsolete - solved many of the CCU construction problems

The Am2910 was so popular that is still exists as a model of a sequencer. Universities build silicon for it, Libraries model it (in Verilog and VHDL), it has been emulated, it has ben built into other larger ICs, in short, it has never left us although AMD no longer supplies a data sheet nor supports it in any way. You cannot buy an Am2910 part. This author still gets requests. |