Refining the CCU

Last Edit November 2, 1996; May 1, 1999; July 7, 2001

Am2910 Instructions

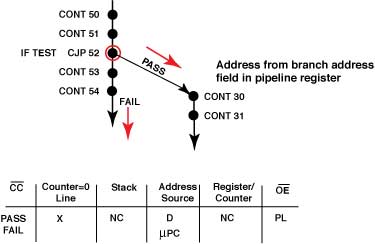

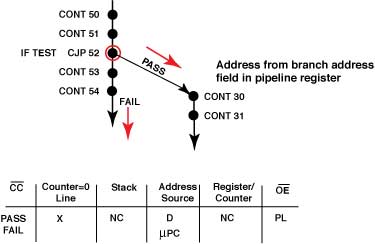

Conditional Jump PL (CJP)

Jump to Pipeline Address If Condition is True Else Continue:

The simplest IF construct used to test for the occurrence of

an interrupt request is Conditional Jump to an address in the

pipeline register. If the CC' input is LOW (the condition is

TRUE), the next address is provided by the pipeline register.

If the CC' is HIGH, the test fails and CJP behaves as CONT instruction.

The pipeline is enabled and the stack and register/counter are

unaffected (see Figure 4-12).

Figure 4-12 Conditional jump pipeline (CJP, 3, 0011)

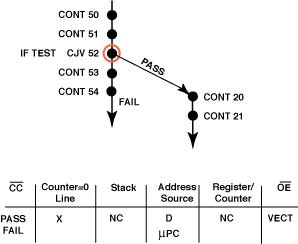

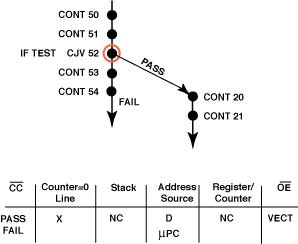

Conditional Jump Vector (CJV)

Jump to Vector Map Address If Condition is True Else Continue:

Another IF construct used to test for the occurrence of an interrupt

request is Conditional Jump Vector. If the CC' input is LOW,

the next address is provided by the vector map. The stack and

register counter are unaffected. The VECT enable is ACTIVE.

If CC' is HIGH, CJV behaves as CONT (see Figure 4-13).

Figure 4-13 Conditional jump vector (CJV, 6, 0110)

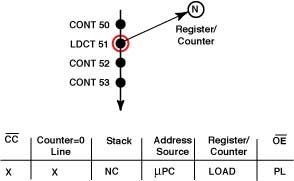

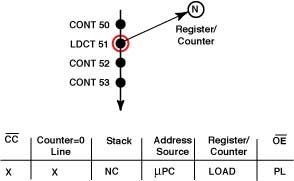

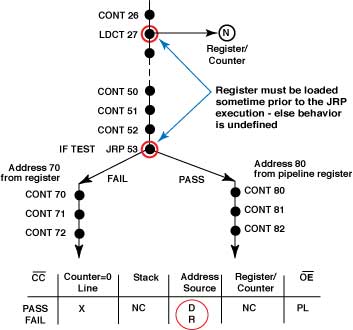

Load Counter and Continue (LDCT)

There are several instructions which use the counter capability

and several which use the register capability of the register/counter.

Each requires that the register/counter be loaded prior to its

execution. Load Counter and Continue provides this ability.

LDCT behaves as a continue statement except that whatever is

gated onto the Di inputs is unconditionally

loaded in the register/counter. The PL' enable is ACITVE; the

stack is unaffected (see Figure 4-14).

Figure 4-14 Load counter and continue (LDCT, C, 1100). This

instruction must be executed before a LOOP instruction or a

jump which used the register.

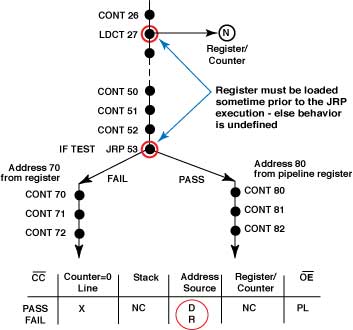

COND Jump R/PL (JRP)

This should have been given the mnemonic CJRP since it is a

conditional statement. (The mnemonic names refer to the Development

System, AmSYS 29, preprogrammed Definition File.) The choice

of where the next address comes from is made based on the CC'

input. If CC' is LOW, the next address is from the piepline

register. If CC' is HIGH, the next address is from the register/counter.

LDCT must have occurred anywhere prior to the execution of

JRP.

Regardless of the test results, the flow is nonsequential.

A branch is taken to one address or another.The PL' enable is

ACTIVE, and the register/counter and the stack are unaffected

(see Figure 4-15).

Figure 4-15 Conditional jump register/pipeline (JRP, 7,

0111).

LDCT must have been executed somewhere ahead of JRP.

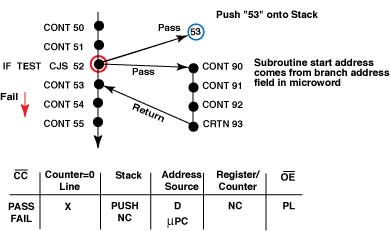

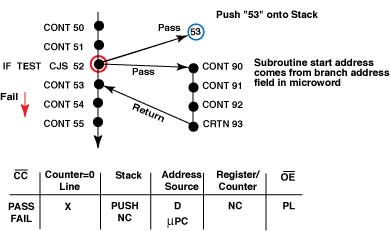

COND JSB PL (CJS)

Microprogram subroutines may be called by the Conditional Jump

Subroutine, with the address of the first microinstruction of

the subroutine given in the pipeline register. IF CC' is LOW,

a branch is taken to the subroutine. The contents of the µPC,

on which the flow diagram of Figure 4-16 is address 53,

are pushed onto the stack and the TOS pointer is incremented.

If CC' is HIGH, CJS behaves as CONT. The PL' enable is ACITVE;

the stack is unaffected.

Figure 4-16 Conditional jump subroutine from pipeline (CJS,

1, 0001)

Continue

|