Bit-Slice Design: Controllers and ALUs

by Donnamaie E. White

Copyright © 1996, 2001, 2002, 2008 Donnamaie E. White

- Pre-Introduction

- Selection of the Implementation

- Microprogramming

- Advantages of LSI

- The 2900 Family

- Language Interrelationships

- Controller Design

- Constructing the CCU

- Sequential Execution

- Multiple Sequences

- Start Addresses

- Mapping PROM

- Unconditional Branch

- Conditional Branch

- Timing Considerations

- Pipelining

- Improved Architecture

3. Adding Programming Support to the Controller

- Expanded Testing

- Subroutines

- Nested Subroutines

- Stack Size

- Loops

- Am29811

- Am2909/11

- CASE Statement (Am29803A)

- Microprogram Memory

- Status Polling

- Interrupt Servicing

- Implementation - Interrupt Request Signals

- Vector Mapping PROM

- Next Address Control

- Am2910

- Am2910 Instructions

- JZ, CONT, JMAP

- CJP, CJV, LDCT, JRP, CJS

- JSRP, CRTN, RPCT, PUSH

- LOOP, CJPP, TWB

- Control Lines

- Interrupt Handling

- Am2914

- Interconnection of the Am2914

6. The ALU and Basic Arithmetic

- Further Enhancements

- Instruction Fields

- Instruction Set Extensions

- Sample Operations

- Arithmetic -- General

- Multiplication with the Am2901

- Am2903 Multiply

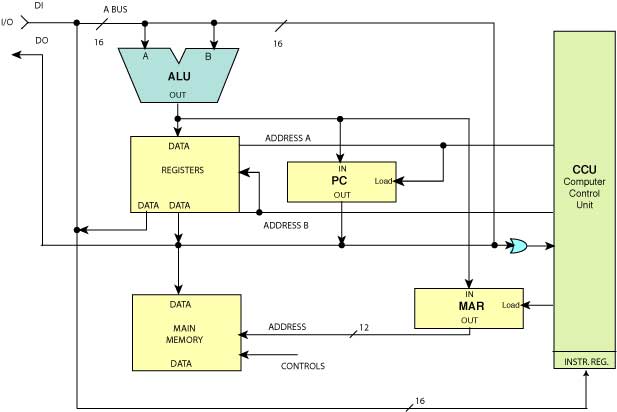

Evolution of the ALULast Edit July 11, 2001 Improving ALU SpeedCurrent Instruction ExecutionReferring to SIMCOM as encoded so far, the number of microcycles required to perform the softyware operation B = A + B (where A and B are memory locations) is fixed at nine (9). The operations invloved are given in Table 5-2.

Table 5-2 Software Operation B = A + B (Memory Addressing)

Scratchpad RegistersIn many instances, with emphasis on the cases where a high volume of computation is performed, an arithmetic operation is performed on the result of a former arithmetic operation or an operation may use the same operands as were used in a former operation. In those cases where the data to be accessed several times or where the result of one operation is to be used several times before it is to be stored into main memory, the availability of scratchpad registers can be shown to improve the system throughput. If the operand data is already in appropriate registers, and if the result is to be kept in one of those registers, the operation RB = RA + RBis performed in three microcycles. To implement this, one format for register operation is:

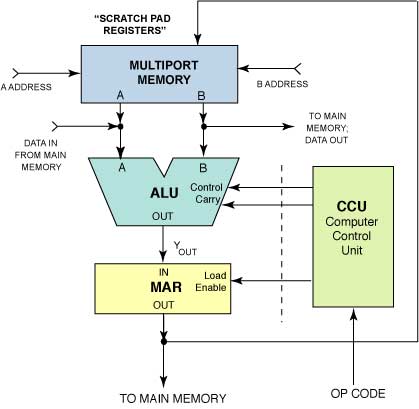

This format allows 256 different register op cpdes and 16 scratchpad registers. This format also requires that the instruction register be as wide as the format (i.e., 16 bits in this example). (The decode of the op code would prevent the MAR being used to perform a memory access if memory addressing and register addressing are used in the same system.) The CCU controls the connection of the register addresses to the scratchpad block via a MUX. Genralized ACCBy using a multiport scratchpad block both source registers may be accessed at once. By using the scratchpad block to replace the single register ACC, 16 different accumulators are possible. The structure is shown in Figure 5-4. Figure 5-4 Register Arithmetic: multiport architecture

The complete microcode would be given as in Table 5-3. Table 5-3 Software Operation RB = RA + RB (Register Addressing)

If all instructions are required to be register oriented, the instruction set could look like that shown in Table 5-4. As a variation, even when any register could be used as the accumulator, some default or implied addressing instructions are desirable for code compaction. These are usually selected to be the most frequently occurring instructions such as load from memory or increment. For SIMCOM, if the R0 register were the default ACC, the load and store instructions would become LDR, addr and STO, addr. As an option, both implied addressing and defined addressing versions of instructions are often included to permit the greatest power adn flexibility in an instruction set. Table 5-4 SIMCOM Register Instruction Set

To perform the register operation itself in one microcycle, the system timing must be such that the instruction cycle is long enough to allow for the read register access, the ALU operation, the write register data, and the address setup time. Generalized PCAnother change can be made to advantage -- the PC can be moved into the scratchpad block (i.e., any register can be the PC register.) This allows arithmetic operations to be performed on the program address as is required in relative addressing, for example, where the PC is added to a base register to find the actual address. Indexed addressing and various other addressing structures are now feasible using high speed register arithmetic. The resulting structure is shown in Figure 5-5. Figure 5-5 Redrawing the Structure

|