Bit-Slice Design: Controllers and ALUs

by Donnamaie E. White

Copyright © 1996, 2001, 2002, 2008 Donnamaie E. White

- Pre-Introduction

- Selection of the Implementation

- Microprogramming

- Advantages of LSI

- The 2900 Family

- Language Interrelationships

- Controller Design

- Constructing the CCU

- Sequential Execution

- Multiple Sequences

- Start Addresses

- Mapping PROM

- Unconditional Branch

- Conditional Branch

- Timing Considerations

- Pipelining

- Improved Architecture

3. Adding Programming Support to the Controller

- Expanded Testing

- Subroutines

- Nested Subroutines

- Stack Size

- Loops

- Am29811

- Am2909/11

- CASE Statement (Am29803A)

- Microprogram Memory

- Status Polling

- Interrupt Servicing

- Implementation - Interrupt Request Signals

- Vector Mapping PROM

- Next Address Control

- Am2910

- Am2910 Instructions

- JZ, CONT, JMAP

- CJP, CJV, LDCT, JRP, CJS

- JSRP, CRTN, RPCT, PUSH

- LOOP, CJPP, TWB

- Control Lines

- Interrupt Handling

- Am2914

- Interconnection of the Am2914

6. The ALU and Basic Arithmetic

- Further Enhancements

- Instruction Fields

- Instruction Set Extensions

- Sample Operations

- Arithmetic -- General

- Multiplication with the Am2901

- Am2903 Multiply

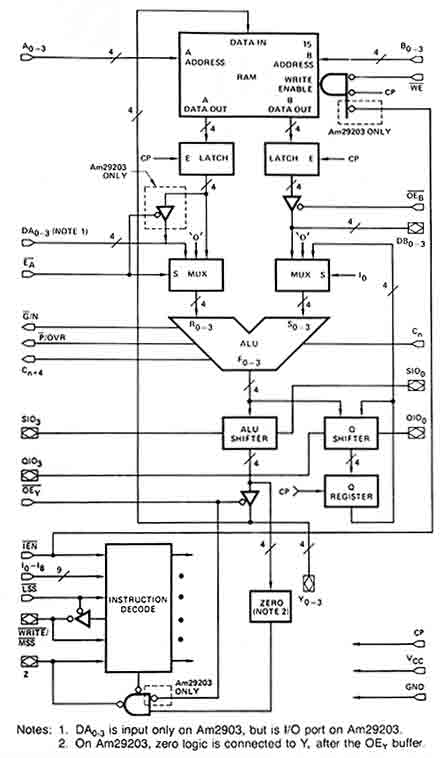

The ALU and Basic ArithmeticLast Edit November 1, 1996; May 1, 1999 ; July 15, 2001 Further EnhancementsIf the Am2901 architecture is altered as follows then the design becomes that of the AMD Superslice™ RALU shown in Figure 6-1:

Figure 6-1 Am2903 RALU

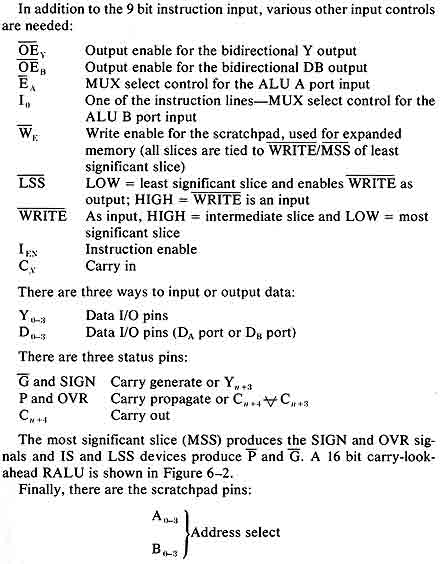

Figure 6-2 Sixteen-bit RALU with carry-lookahead

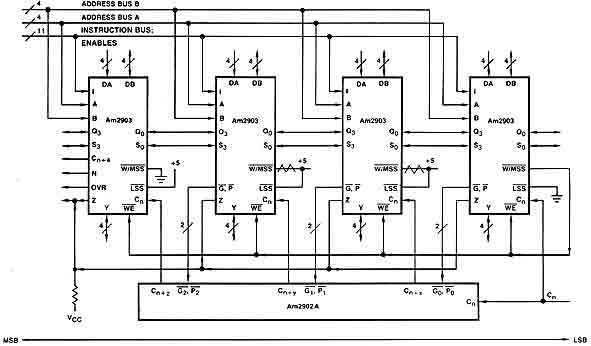

The Am2903 is more powerful than the Am2901. It has a richer instruction set, including nine special functions which use user-inaccessible internal controls to facilitate operations such as two's complement multiply, sign extend, and normalization. It can be used with an expanded scratchpad memory so that the RALU is no longer limited to 16 registers. The ability to identify a slice as to its significance contributes to the instructional power available. The Am29203 will [it did] feature additional special instructions (BCD arithmetic). Like the Am2900 family in general, the Am2903 is a low-power Schottky device with tristate outputs. The Am2903 is in a 48-pin package. The Am2903A and the Am29203 are ECL internal and TTL external for higher speeds. [Remember that this was the 1970s-1980s.] Instruction FieldsThe basic 9-bit instruction field is broken up into subfields differently from the Am2901:

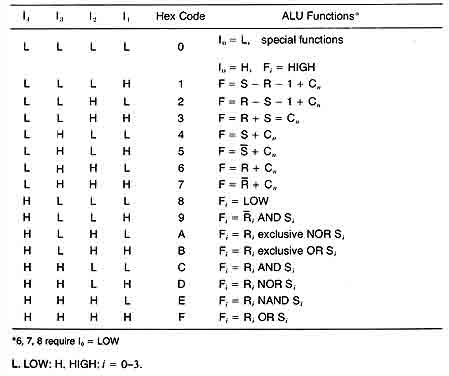

Instruction Set ExtensionsThe basic arithmetic and logic function set of the Am2903 has several extensions to that of the Am2901, including all HIGH, all LOW and the logical NAND and NOR functions (Table 6-1). Table 6-1 Am2903 ALU Functions

ShiftingThere are two types of shifting possible owing to the identification of the significance of the slices. The logical shift shifts through all bit positions. The arithmetic shift shifts around the most significant bit position, i.e., the sign is undisturbed. The Am2903 data sheet provides a detailed table for the destination-shift control. Note that the source - ALU and destination control tables are valid only if: For the case: the special functions override the normal chip operations, with I5-8 as the function select control field. Three-Address OperationThe Am2903 may be used to perform a three-address operation. The given A-B addresses are used as the source addresses and a third address used as the destination. The second and third addresses are input to a MUX whose selection is under clock control such that the B address is stable for the read and the C address is stable for the write. The third address must be in a register. The actual WRITE takes place on the rising edge of the clock. See the Am2903 data sheet for control details.

|